インテルが発表したメニーコア時代のコプロセッサ「Xeon Phi」:初代地球シミュレータを2ラックで

インテルが、並列処理向けのコプロセッサを発表。x86アーキテクチャによるメニーコアはGPGPUによる並列処理よりも、既存のソフトウェア資産が活用できるという。

インテルは2012年11月12日、コプロセッサ「Xeon Phi」を発表した。2013年1月28日にXeon Phi 5110Pが、2013年上半期中にはさらに3100ファミリーが投入される予定だ。

現時点で、国内メーカーではデル、HP、日立、富士通、NEC、IBM、SGI、クレイがXeon Phi搭載製品の出荷を予定している。

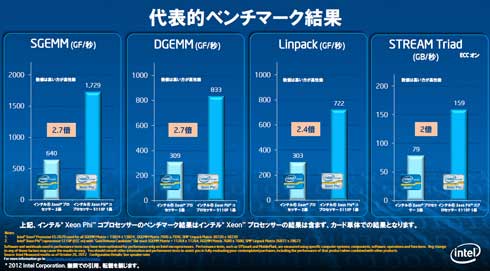

5110Pはピーク時性能として1.011TFLOPSの倍精度演算が可能で、8GB GDDR5メモリを搭載、320Gbpsの帯域幅を持つ。60コア、240スレッドの並列が可能だ。一方の3100ファミリは1TFLOPSの倍精度演算性能、6GB GDDR5メモリを搭載、240Gbpsの帯域幅となっている。

「40TFLOPSの処理性能であった、320ラックの初代地球シミュレータ(2002年稼働)と同等の性能を2ラックで実現できる」(インテル クラウド・コンピューティング事業本部 事業開発本部 本部長 岡崎覚氏)

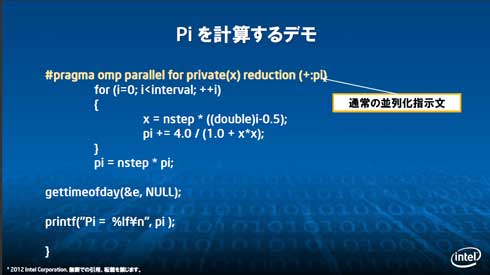

物理シミュレーションなどの工学系の計算では、CやC++、Fortranなどの言語で書かれた、並列処理を前提としたものが少なくない。

最近では、NVIDIAが提供するCUDAライブラリを採用した並列プログラムなど、GPGPUによる並列プログラミングが注目を集めている。処理性能を高められる一方で、既存資産の移植にはCUDAプログラミングのスキルが必要となる。

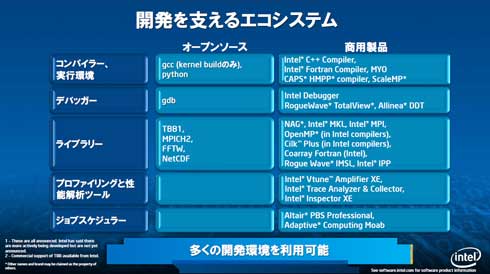

Xeon Phiコプロセッサは、Xeon向けと共通の開発環境で利用できる点が特徴となっている。このため、実行するだけならば、旧資産をほぼそのまま流用可能だという。無論、vTuneなどのチューニングソフトウェアを活用し、より処理性能を高めることも可能だ。この部分をGPGPU向けに大幅に改編することなく、そのまま実施できる点が利点となっている。

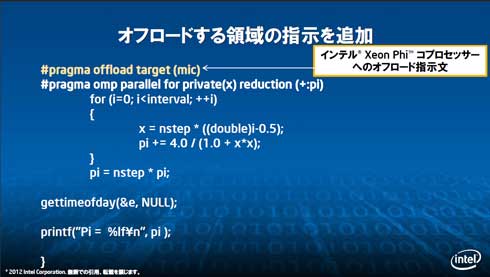

明示的にオフロード実行させる際のコード例 ソースコード内でXeon Phi側で処理したい部分を指定する「オフロード実行」の例。この状態で対応コンパイラでコンパイルすれば、そのまま実行時に指定の処理がCPUからXeon Phi側に渡される

インテルではこれに併せて、Xeon Phiコプロセッサ対応版の「Intel Parallel Studio XE 2013」「Intel Cluster Studio XE 2013」も発売する。その他にもサードパーティ製コンパイラの対応表明も行われている。

なお、Xeon Phiはあくまでもコプロセッサであるため、動作にはホストCPUとしてXeonが必要である。

インテルでは、今後、需要が増えると見込まれる薬品開発やエネルギー、自然環境のモデリングなどの物理・工学系の分野や、金融、製造業などの分野での採用に期待を寄せている。

Copyright © ITmedia, Inc. All Rights Reserved.