スパコン「京」の100倍の処理性能へ、富士通がArmベースのプロセッサを開発:AI処理に向け整数演算性能も向上

富士通はスーパーコンピュータ「京」の後継機に実装するプロセッサ「A64FX」の詳細を公表した。Arm命令セットアーキテクチャを採用し、スーパーコンピュータ向けの拡張命令を実装した。半精度浮動小数点演算や整数演算性能も向上させた。

富士通は2018年8月22日、理研と共同開発するスーパーコンピュータ「京」の後継機に実装するプロセッサ「A64FX」の詳細を発表した。同年8月19〜21日に米カリフォルニア州クパチーノ、米IEEEが主催した「Hot Chips 30」で公開したもの。

2021年ごろの京後継機の供用開始を予定しており、富士通は、A64FXの試作品による機能試験を既に進めている。

京は2011年に、浮動小数点演算性能10.51PFLOPS(ペタフロップス)を記録し、世界のスーパーコンピュータをランク付けするTOP500リストで世界一になった。

A64FXを搭載した後継機は、最大で京の100倍のアプリケーション実行性能と、30M〜40Mワットの低消費電力を目指ししている。

倍精度浮動小数点演算のピーク性能は2.7TFLOPS(テラフロップス)以上。単精度では2倍の5.4TFLOPS以上、半精度では4倍の10.8TFLOPS以上の浮動小数点演算性能が得られる。

さらにビッグデータ解析やAI処理に向けて、16bitや8bitの整数演算性能も強化した。16bit整数演算では10.8TOPS(Tera Operations Per Second)以上、8bit整数演算では21.6TOPS以上の性能が得られる。富士通では、コンピュータシミュレーションだけにとどまらず、幅広い分野に適応可能だとしている。

Arm命令セットアーキテクチャを採用

A64FXでは、Arm命令セットアーキテクチャを採用し、スーパーコンピュータ向けの拡張命令を実装した。「Armv8-A命令セットアーキテクチャのスーパーコンピュータ向け拡張である「SVE(Scalable Vector Extension)」を、世界で初めて採用したという。

命令セットアーキテクチャとプロセッサの内部構造であるマイクロアーキテクチャは、独立に設計可能だ。富士通は、A64FXのマイクロアーキテクチャを、同社がこれまでスーパーコンピュータやメインフレーム、UNIXサーバで培った技術を発展させて開発したとしている。

A64FXに集積したトランジスタ数は約87億個。最小加工幅7ナノメートルのFinFET(Fin Field-Effect Transistor)を用いる。

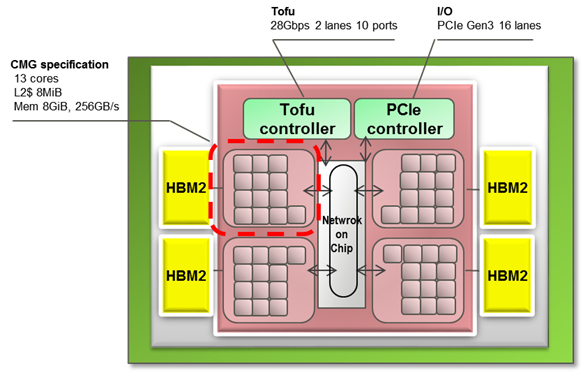

A64FXプロセッサは4個のCMG(Core Memory Group)で構成される。1個のCMG当たり12個のコンピューティングコアと1個のアシスタントコア、8MBの2次キャッシュメモリ、8GBの主記憶を集積した。つまり、1プロセッサ当たりのコア数は、コンピューティングコアが48個、アシスタントコアが4個、メモリは32GBとなる。

京の特徴である高いメモリのバンド幅(データ転送速度)を強化しつつ、プロセッサ同士を、「Tofuインターコネクト」と呼ぶ富士通独自のバスで直結し、並列性能を向上させている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

目指すは世界最大級のArmスパコン――HPE、米エネルギー省との共同による「Astra」開発計画を発表

目指すは世界最大級のArmスパコン――HPE、米エネルギー省との共同による「Astra」開発計画を発表

HPEは米エネルギー省および同省サンディア国立研究所と協力し、世界最大級のArmスーパーコンピュータ「Astra」を開発する。 第202回 スパコンの新しい潮流は人工知能にあり?

第202回 スパコンの新しい潮流は人工知能にあり?

スーパーコンピュータ関連の発表が続いている。その多くが「人工知能」をターゲットにしているようだ。人工知能向けのスーパーコンピュータとはどのようなものなのか、最近の発表から見ていこう。 東京工業大学のAIスパコン「TSUBAME3.0」計画が始動、2017年夏稼働へ

東京工業大学のAIスパコン「TSUBAME3.0」計画が始動、2017年夏稼働へ

東京工業大学が次世代スーパーコンピュータ「TSUBAME3.0」の開発計画を発表。NVIDIAのGPU「Tesla P100」を採用し、64ビットの倍精度性能だけでなく、AIやビッグデータ分野などに向けた47.2PFLOPSの半精度(16ビット)浮動小数点演算性能も目指す。