機械学習/Deep Learningの仕事が増える2017年、ソフトウェアエンジニアがFPGAを学ぶべき理由:PythonコードからFPGAを生成、深層学習したDNNをハードウェアに

ソフトウェアエンジニアがFPGAを使うハードルがさらに下がってきている。ソフトウェア開発者の立場でFPGAに取り組むイベント「FPGAエクストリーム・コンピューティング」を主宰する佐藤一憲氏、FPGAの高位合成によるディープラーニングについて研究している東京工業大学の中原啓貴氏、そしてFPGAベンダーであるザイリンクスの神保直弘氏が、急激に常識が変わりつつあるFPGAの動向を語り合った。

ソフトウェアエンジニアがFPGA(field-programmable gate array)を使うハードルがさらに下がってきている。クラウドサービスでFPGAを活用できたり、Pythonで記述したニューラルネットワークをFPGAに高位合成できる研究成果が出てきたりしているのだ。

ソフトウェア開発者の立場でFPGAに取り組むイベント「FPGAエクストリーム・コンピューティング」を主宰する佐藤一憲氏、FPGAの高位合成によるディープラーニングについて研究している東京工業大学の中原啓貴氏(中原研究室)、そしてFPGAベンダーであるザイリンクスの神保直弘氏が、急激に常識が変わりつつあるFPGAの動向を語り合った。

座談会出席者(左から神保直弘氏(ザイリンクス グローバルセールスアンドマーケットマーケティング部 シニアマネージャー)、中原啓貴氏(東京工業大学 工学院 情報通信系 准教授)、佐藤一憲氏(IT企業勤務、「FPGAエクストリーム・コンピューティング」主宰))

座談会出席者(左から神保直弘氏(ザイリンクス グローバルセールスアンドマーケットマーケティング部 シニアマネージャー)、中原啓貴氏(東京工業大学 工学院 情報通信系 准教授)、佐藤一憲氏(IT企業勤務、「FPGAエクストリーム・コンピューティング」主宰))本稿では座談会の中から、ソフトウェアエンジニアにFPGAや高位合成が求められる現状、そして、今後どのようなツールを使うべきか、ソフトウェアエンジニアがFPGAに取り組む際の課題などについてお伝えする。

(以下、敬称略)

コードからいきなりFPGAを作る、高位合成が主流の時代

──佐藤さん、神保さんは前回の座談会にも登場しています。中原先生には、自己紹介をお願いできますか?

中原 2016年4月から東京工業大学に移りましたが、それまで鹿児島大学、愛媛大学にいました。実はFPGAのHDL(ハードウェア記述言語:Hardware description language)を書いたのは学位を取ってからで、ルーターのパケット処理のプロトタイプとしてFPGAを使ったのが最初です。FPGAでパケット分類器を作ったらソフトウェアよりも20倍ほど速かったんですね。あの速さは魅力的でした。Xilinxのボードを最初に買ったのは「Spartan-3 スタータ キット」。あれをいじってHDLを覚えました。

最近は大学が忙しくてHDLを書く時間が取れず、2015年ごろから高位合成ばかりです。Xilinxの高位合成ツール「Vivado HLS」(High-Level Synthesis)だと一発で合成できる。「こんなに簡単なんだ」と思いました。大学では、(FPGAで通常使うハードウェア記述言語)Verilog HDLは使わず、高位合成しか教えていません。もうソフトウェアのコードを書く感覚でFPGAを使っている学生ばかりです。

佐藤 すごい。新世代ですね。

中原 うちの学生には、XORゲートの真理値は書けなくても、FPGA向けのディープラーニングの設計はできる者がいます。常識がすごく変わってきています。

神保 いや、そこまで新しいのは中原先生のところぐらいです。

佐藤 中原先生のように某国民的ゲームマシンを1週間でFPGAに落とせる人は特殊だと思います。

──中原先生がFPGAでディープラーニングに取り組んだのは、何かきっかけがありましたか?

中原 2014年ぐらいに、ディープラーニングの研究が盛んになりましたが、ディープラーニングで先行している人がGPUユーザーばかりで、その中に割って入るのは難しいと考えました。でもFPGAでやっている研究者はほとんどいなかった。これはチャンスだと思い、取り組みました。

実は、最近の「人工知能」ブームでディープラーニングが注目される前の2005年ごろに、3層ニューラルネットを手掛けていて、演算精度はそれほどいらないことは分かっていました。「GPUのアーキテクチャは機械学習に向いている」という考え方もありましたが、FPGAと固定小数点の論理回路でけっこういける。そう考えました。

──どんな成果が得られましたか?

中原 ディープラーニングで演算精度を1ビットまで落とすことに成功しました。認識精度が数%低下することを許容すると、ハードウェア量を約5分の1に下げることができます。

FPGAの高位合成でディープラーニングを行えるツールは、われわれと、後は世界中で数例ぐらいしかないのではないでしょうか。ボタンを押すと、学習させたニューラルネットワークがFPGAに落ちる。うまくいけば、2017年度から実用化できそうです。

──ディープラーニングのライブラリは何が使えますか?

中原 TensorFlow、それにCaffe、Chainerなどを使えます。それに会社や部署によっていろいろなフレームワークを使うので、複数のフレームワークに対応しています。Pythonでコードを書いて、ある工夫をしてC++に落とし込んで、Xilinxのツールに入れると動きます。

──FPGAでディープラーニングを手掛けるのに、Pythonが書ければOKなんですか?

中原 OKです。C言語すら書けなくていい。

神保 Pythonで設計するというお話のように、FPGAの使い手の中にC/C++より上位言語で設計する人が出てきてくれているのは、ベンダーとしてはまさに狙い通りでありがたいことです。

10年前を振り返ると、かなりの人数のハードウェアエンジニアが世の中にいて、その人たちを相手にビジネスをしていました。今は理系の大学に入って工学部を選んでハードウェアを勉強する学生は少なくなっている。世界的に見ても同じ傾向があります。だからFPGAに親しんでもらうには、今の主流のプログラミング言語で開発できるようにしないと。

以前は開発ツールのベンダーが高位合成ツールを作っていました。しかしFPGA向けではなくASIC(特定用途向け集積回路:Application Specific Integrated Circuit)向けが中心だったため、FPGAに最適化したコードをなかなか生成してくれなかった。そこで自社でツールを持つべきだと考え、高位合成ツール「AutoESL」のベンダーを買収するなどして、高位言語向けコンパイラの整備に注力したのです。

中原 実は悩みがありまして。大学の天文学者のチームと共同研究をしているのですが、以前はFortranやCのコードをFPGAにすれば良かった。ところが最近は(統計解析機能が強力な)R言語や(言語仕様が最新過ぎる)C++ 17などでコードを書いてくる。彼らから見れば通常のC/C++は下位言語です。だから早く高位な言語からの合成ができるようになってほしいと。

佐藤 私がやっているエクストリームコンピューティング勉強会のサブセットで「高位合成友の会」というのがあって、そこではVivado HLSのような高位合成ツールを自分たちで作っている人もいます。例えばJavaScriptベースの高位合成ツールです。ハードウェアとソフトウェアの両方を知っている人からすると、C/C++は高級言語ではないので、PythonやTensorFlowのようなドメインスペシフィックなものを使いたいという流れは起きていると思います。

ムーアの法則の終焉に伴い、FPGAの出番が増える

──2015年に引き続き、2016年の1年間で見ても、FPGA関連で目立つ動きがありました。Amazon Web ServicesのクラウドでFPGAをサポートした「F1インスタンス」が登場したり、Intelが、買収したFPGAベンダーAlteraと製品の統合を進めたり、ミラクル・リナックスがFPGAで文字列分割処理を最大10倍高速化するフレームワークを開発したり、日立製作所がFPGAを利用してデータ分析速度を最大100倍に高速化する技術を開発したと発表したりしています。

佐藤 ムーアの法則が終わり、CPUだけではこれ以上の急激な高速化が望めないからです。問題を速く解くには専用ハードウェアが必要になってきます。それも、機械学習や暗号化のようにアプリケーションごとに違うハードウェアが出てくる。

神保 米国ではビデオストリーミングが主流になっていて、1つのコンテンツを携帯電話で見たり、家庭にある4Kテレビで見たりします。そこでリアルタイムでストリーミングをしながら、それぞれ最適化したサイズで映像を送り出す。そのために、ある解像度で事前に圧縮しておくのではなく、リアルタイムの圧縮(エンコーディング)が求められていて、そこでサーバサイドにFPGAなどで専用ハードウェアを利用する考え方が出てきています。

──今後、FPGAは最短時間でハードウェアを作る手法との位置付けになると思いますが、そもそも、短い時間で作らないといけない背景についても教えてください。

中原 人工知能、機械学習/ディープラーニングの分野ではアルゴリズムが日進月歩で早い者勝ちのレッドオーシャンになっています。しかし、論文を書いても刊行されるまで半年はかかるため、学会に投稿する前にWebのアーカイブに上げて証拠を残すような状況になっています。そこでWebに載せると、そのアルゴリズムを「評価した」「改善した」という報告が数日後に来る。そういうレベルです。FPGAの主要な国際会議も年に4回で、3カ月で新しい手法や改良手法が出て来る。

佐藤 そこがFPGAの重要なところです。ASICだとリスクが大きい(注1)。ASICは作って動かすのに1年かかるけど、FPGAだったら明日から使えます。ムーアの法則が有効だった時代の発想のままでは競争に負けてしまう。ハードウェアによる並列化の恩恵を生かさないと。

注1:ASICは、専用回路なのでFPGAより高速に動作するが、設計と製造にかかる時間とコストは膨大になる

中原 ディープラーニングでいえば、DNN(Deep Neural Network)は認識精度が図抜けて高いですが、その代償としては計算量が大きくなる。積和演算、特に乗算が桁違いに多い。組み込み機器で使う場合はリアルタイム性が重要になります。幸いなことに、ディープラーニングで使う行列計算は行列の行ごと、列ごとに独立に計算できるので、並列計算できるようにパスを設計できます。GPUはパスが固定です。FPGAは柔軟にパスを作って並列に並べることができるところが、GPUにはない魅力です。また、演算精度をカスタムにできるのも大きい。

GPUの弱点の1つには、if文が苦手なこともあります。FPGAを使う人はアーキテクチャを自分で作れる。例えば、if文の高速化が必要ならマルチプレクサを並べる。例えば、(機械学習のアルゴリズムの1つである)「ランダムフォレスト法」はGPUだと性能が出ませんが、FPGAはif文を並べた回路を作れるので高性能にできます。

佐藤 それはすごいですね!

中原 GPUだとスケールしないんです。FPGAだとif文のお化けがアンバランスになりますが、作れます。これはうちの学生が2017年1月に発表した内容です。

佐藤 ぼやぼやしていると置いていかれるという危機感すら覚える話ですね。でもワクワクします。

中原 現在は高速化の他の方法も探しているところです。1つは、今まで2次元つまり、縦横でレイアウトしていた半導体チップを、3次元、つまり高さの方向にもレイアウトできないかということ。例えば慶應義塾大学の黒田先生はチップ中のトランジスタをスタッキング(積層集積)する研究をしています。課題は幾つかあって、チップ内の通信をどうするか、どれだけチップを均一に薄くできるか、それに熱をどう逃がすか。通信については無線通信でいけそうな見通しであると伺っています。

FPGAで手軽に遊べることが、実は重要

佐藤 個人的な意見ですが、FPGAで注目したいことが大きく2つあります。1つは、ご指摘のようにビジネスの観点から見てFPGAが面白い状況だということ。そしてもう1つは、ホビーとしても面白いということです。

昔は、電子回路を組むには“はんだ”付けをしないといけないし、配線や“はんだ”付けのやり方を間違えるとすぐ壊れてしまった。TTL(Transistor Transistor Logic)で論理回路を組んで「Lチカ」(LED点灯)をするだけで大変でした。FPGAなら、ソフトウェア的な再構成で簡単にデジタル回路を組んで加算機を組み立ててCPUを作るまでが“はんだ”付けなしでできます。

子どもの頃に「電子ブロック」を親に買ってもらったのですが、あれは値段に比例して部品の数が増えるんです。ところがFPGAだとロジックセルの数が桁違いに多い。1万円出すと1万ゲート、2万ゲートの製品が買える。これならCPUも作れちゃう。ゲート数が多いと、高位合成で組める回路の幅も広がります。

何十年か前のコンピュータアーキテクチャの世界は、RISC(Reduced Instruction Set Computer)とCISC(Complex Instruction Set Computer)の論争があるなどが面白かった。その後、世の中がIntelチップに収束したので、ホビイストにとってはコンピュータアーキテクチャに思い入れがあってもどうにもできない。ところがFPGAだと、例えばSmalltalk言語のバイトコードを実行するプロセッサや、何十個も演算器があるプロセッサを、作ろうと思えば作れる。ワクワク感がよみがえる感じがします。

最近流行した言葉で「破壊的イノベーション」というのがありますが、破壊的イノベーションは最初はオモチャにしか見えないんです。「オモチャみたいに遊べるFPGAから、とんでもなくイノベーティブなものが出てくるんじゃないかな」と期待しています。

──ホビーからイノベーションが生まれた例には、パーソナルコンピュータ(PC)がありました。FPGAに大勢の人がホビーのように取り組むことで、専門家にとっても予想外のものが出て来る可能性がありますね。

神保 ベンダーの立場からは「FPGAといえばハード屋さんが触るもの」という世界から飛び出して、ソフトウェアエンジニアをはじめ、多種多様なタイプのエンジニアが「ツールの1つ」として使ってもらえるものになるといいなと思っています。ユーザーグループ活動としてコミュニティーが出来上がりつつあります。

オープンソースが支えるSoC搭載評価用ボードPYNQ

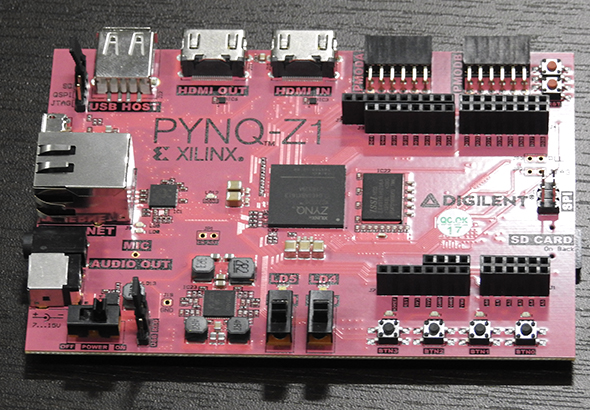

──ホビイストやソフトウェアエンジニア向けのボードとして、中原先生に持参していただいた、「PYNQ(Python Productivity for Zynq)」があると思います。これについて、簡単に説明をお願いできますか?

神保 FPGA関連製品には、まずFPGAだけが載っているタイプのデバイスと、ARMコアのCPUと周辺回路が一緒に載っているデバイスがあります。後者をSoC(System on Chip)タイプといいます。PYNQは、SoCタイプの「Zynq」を搭載して、Pythonとそのライブラリで、CPUとFPGAをプログラミングできるようにした評価用ボードです。CPUでソフトウェアを動かして、「このロジックはぜひハードウェアに落としたい」という部分だけをFPGAに落として組み合わせることができます。

もう1つ、PYNQはオープンソースのプロジェクトです。時代の流れとして、「いろいろなタイプのエンジニアが参加できる形のオープンソースで作っていきたい」という思いがあります。

佐藤 FPGAで何か気の利いたことをやらせるには、ソフトウェアとハードウェアの両方を作らないといけません。Cの開発環境やARM用コンパイラなどをゼロからそろえて使い方をマスターするのは手間が掛かります。その点、PYNQは、私たちが普段使っているPython開発環境を使って4〜5行もコードを書けば、もうFPGAのロジックと連携して使えちゃう。そこがすごい。

中原 PYNQの「アカデミック向けには65ドル」(一般向けは229ドル)という値段は安いですね。1万円を超えると心理的に手が出しにくい。「RasPi感覚」で使えます(注2)。それにArduinoのシールドが刺さるので、Arduinoのエコシステムを使えるのもいいですね(注3)。

注2:RasPi(Raspberry Pi)はARMチップ搭載でLinuxが動く低価格&超小型ボードとして人気

注3:ArduinoはメディアアートやMakerムーブメントなどの分野で人気の制御用ボードで、シールドは小型の回路基板をArduinoのメインボード上のコネクタで接続して機能を拡張できる製品群。入出力やセンサー関連の品揃えが豊富

大学のゼミでもPYNQは使っていまして、数式をその場で動かせるデモができます。プログラミングしながらその原理となる数式を追えるんですよ。また、内部では(Linuxディストリビューションの)Ubuntuが動いています。

佐藤 いきなりLinuxが動くのはうれしいですよね!

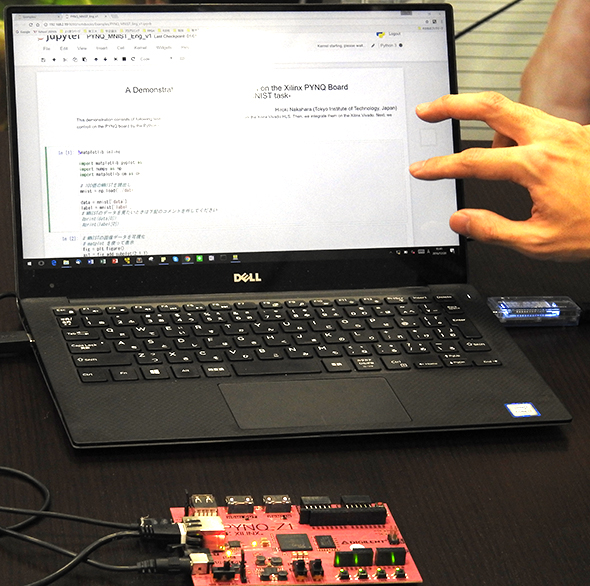

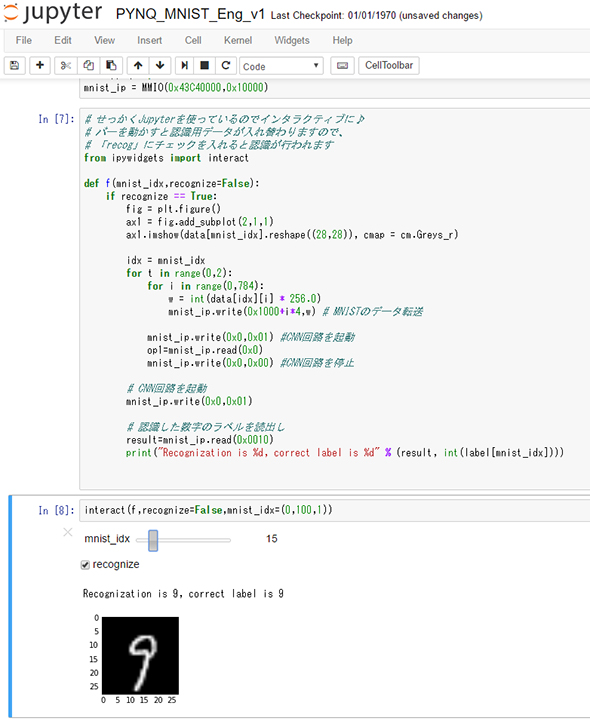

中原 そこで、Jupyter Notebook経由でFPGAを使います(注4)。

注4:Jupyter NotebookはWebブラウザベースで手軽に使える多機能なPythonコード実行環境(参考)

佐藤 Jupyter Notebookがまたうれしいんです。ドキュメントとソースコードが一体化していて。

──中原先生、実際にJupyter NotebookとPYNQを使ったデモを見せていただけますか?

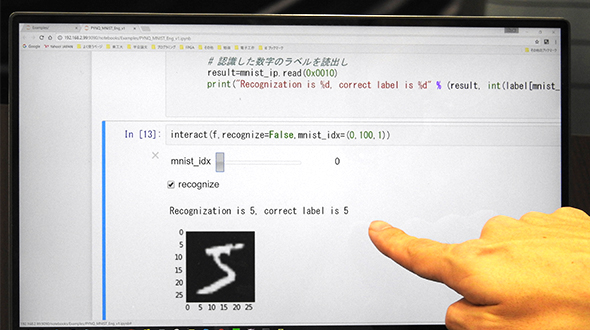

中原 これは2016年12月に中国の国際会議FPT 2016で披露したデモなんですが、注目を浴びて2時間ほどワイワイと質疑をしていました。ポスターセッションの中でピンク色のボードを出していたのが目立った(笑)。5層のCNN(Convolutional Neural Net)が入っていまして、Pythonコードの中でちょっとパッケージをインポートして、番地を書くだけ。2行か3行で動かせます。

佐藤 ここで強調したいのが、ハードウェアつまりFPGAを作る人と、ソフトウェアを作る人の協業がすごく簡単になるということです。ソフトウェアの人がビットストリーム(FPGAをコンフィギュレーションするためのデータ)をほんの数行のコードで読み込める。

中原 「PCとFPGAの間でデータを、どうやりとりするのか」という質問がよく来ます。従来は、そこが障壁になっていましたが、PYNQの場合はUbuntuが入っているので、コンフィギュレーションデータは仮想ハードディスクに送り、認識用データはAXI(Advanced eXtensible Interface)バスを通してARMプロセッサから送るだけです。このCNNで約95%の認識率が出ています。

それと、PYNQをモバイルバッテリーで動かして、電力計の表示も見てもらって、FPGAでDNNを動かすと消費電力が少ないというデモをしました。

佐藤 電力消費は?

中原 今、約5V×0.5Aで250mWぐらいです。

佐藤 RasPiでも今は3〜4Wぐらいですよね。

中原 電力対性能比という観点で考えると、CPUやGPUでDNNを処理するやり方に比べて数百倍の差があります。

佐藤 普通のドローンだとRasPiもGPUも載せるのが厳しいですが、これなら載せられます。5層のDNNなので、例えば「人の顔か、猫の顔かを見分ける」認識なら軽くできます。性能面でも、例えばRasPiより80倍ぐらいは速くできる。

中原 これの面白いところは、ARMコアでUbuntuが動いている間に、FPGAの書き換えができることです。ユーザーごとに違う回路を試す使い方も可能になります。

佐藤 仮想化みたいだ。

中原 それを意識させないようなフレームワークが出てくるといいですね。

ソフトウェアエンジニアがFPGAに取り組む際の課題

──PYNQのようなツールが出てきてはいますが、ソフトウェアエンジニアにとって、まだまだハードル、課題があると思います。具体的には、どのようなことが課題になっていくのでしょうか?

中原 ソフトウェアの分野では決定的な教科書がたくさんありますが、FPGAの分野ではまだ出ていません。独学する場合のハードルがまだ高いので、そこを下げないといけません。学術書ですけど、2017年には『FPGAの原理と構成』第2版(オーム社刊)が出ます。ツールの本はかなり充実してきましたが、高位合成の本も欲しいですね。

神保 2017年春頃には、ザイリンクスのエンジニアも執筆に関わっている高位合成の本が出ます。

佐藤 従来の高位合成ツールは高価でしたが、Vivado HLSは無償です。書籍が出てくるとさらにいいですね。技術普及の意味で、低価格ボードや無償ツール、それに書籍には意味があります。

中原 もう1つ、PYNQなどを使うと書いたコードはハードウェアに落とせますが、それが高性能になるかどうかというと、工夫が必要です。FPGAをよく理解してコードを書かないと性能が出ません。例えばFPGAチップ上のメモリにアクセスするのはいいですが、メインメモリへのアクセスを多用すると、そこはバンド幅が遅いので、全体的にも遅くなってしまう原因になります。そうした依存性がない、癖がないコードを書くところが1つのハードルになります。

佐藤 FPGAを使いこなすスキルを身に付ける一方で、アプリケーションの高速化手法は、FPGA以外にもありますよね。通常のCPUにも並列処理をするSIMD(Single Instruction Multiple Data)命令、MIMD(Multiple Instruction Multiple Data)命令があるし、GPUで高速化するやり方もある。FPGA、CPU、GPUの3通りの手法の最適化を検討できて、その上で「一番良いのはFPGAだ」と評価できる人はごく限られています。ホビイストのレベルと、仕事で使うレベルの間にある壁ですね。

──仕事で使うというと、エンタープライズ分野での利用事例にはどのようなものがあるのでしょうか?

佐藤 エンタープライズの分野では、IBMのNetezzaテクノロジーが応用例です。データウェアハウス向けのハードウェア製品で、内部ではFPGAが使われています。

「データベース管理システムでは、クエリの処理にはCPUサイクルの6%しか使っていない」というデータがあって、それ以外の処理をハードウェアで実行できると処理性能や電力効率が変わるはずです。

中原 金融分野では、FPGAにNIC(Network Interface Card)を直結して高頻度取引(HFT)に使う需要があります。HDLが書けると、収入が3倍ぐらいになるそうです。

神保 「FinTech」といわれる分野ですね。最近は、データサイエンティストの作った数式やアルゴリズムをエンジニアが理解してコードに落とし込む需要が多いそうです。微積分を含む数式を、for文を使ったコードにするとか。金融工学以外でもビッグデータ分析の世界では、アルゴリズムをハードウェアにまで落とし込める理解力のあるエンジニアが求められています。

佐藤 日本にはHDLを書ける人がたくさんいますが、さらに英語と金融系のスキルを加えれば、収入が大幅に増える人も出てくるでしょうね。

──ありがとうございました。

関連記事

Fluentd、Memcached、IoT、ドローン、機械学習、映像解析――ソフトとハードを隔てる壁が壊れつつある今、ITエンジニアは現実的に何ができるようになるのか

Fluentd、Memcached、IoT、ドローン、機械学習、映像解析――ソフトとハードを隔てる壁が壊れつつある今、ITエンジニアは現実的に何ができるようになるのか

これまでになく、ソフトウェアエンジニアの間でFPGAへの関心が高まる昨今、本企画では、FPGAベンダーであるザイリンクスの神保直弘氏、ソフトウェア開発者の立場でFPGAに取り組むイベント「FPGAエクストリーム・コンピューティング」を主宰する佐藤一憲氏、そしてブログサイト「FPGAの部屋」を書き続けてきた小野雅晃氏に集まってもらい、座談会を実施した。「FPGAネイティブ世代」の登場により、ソフトウェアとハードウェアの間に在った壁が壊されようとしている現状をお伝えする。 特定処理の高速化をFPGAで実現――ザイリンクス、IBM

特定処理の高速化をFPGAで実現――ザイリンクス、IBM

「OpenStack」や「Docker」「Spark」といったデータセンターアーキテクチャ向けに、特定の処理にFPGAをアクセラレーターとして利用する仕組みをIBMが正式に展開する。コンピューティングリソースの負荷を低減し、エネルギー効率を高める。 ザイリンクス、OpenCL、C/C++でFPGAアクセラレーションを行う開発環境最新版のリリースを発表

ザイリンクス、OpenCL、C/C++でFPGAアクセラレーションを行う開発環境最新版のリリースを発表

ザイリンクスは5月26日(米国時間)、FPGAを使用したアクセラレーター開発環境の最新版「SDAccel開発環境2015.1」のリリースを発表した。最新版では、統合開発環境の機能が強化され、対応ライブラリも拡充される。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:ザイリンクス株式会社

アイティメディア営業企画/制作:@IT 編集部/掲載内容有効期限:2017年3月1日

東京工業大学 工学院 情報通信系 准教授 中原啓貴氏

東京工業大学 工学院 情報通信系 准教授 中原啓貴氏 ザイリンクス グローバルセールスアンドマーケットマーケティング部 シニアマネージャー 神保直弘氏

ザイリンクス グローバルセールスアンドマーケットマーケティング部 シニアマネージャー 神保直弘氏 佐藤一憲氏(IT企業勤務、「FPGAエクストリーム・コンピューティング」主宰)

佐藤一憲氏(IT企業勤務、「FPGAエクストリーム・コンピューティング」主宰) 中原氏のPYNQ-Z1ボード

中原氏のPYNQ-Z1ボード Jupyter NotebookとPYNQを使ったデモ1(連携開始)

Jupyter NotebookとPYNQを使ったデモ1(連携開始) Jupyter NotebookとPYNQを使ったデモ2(「5」という数字が書かれた画像を認識している)

Jupyter NotebookとPYNQを使ったデモ2(「5」という数字が書かれた画像を認識している) Jupyter NotebookとPYNQを使ったデモ3(Pythonコード)

Jupyter NotebookとPYNQを使ったデモ3(Pythonコード) Jupyter NotebookとPYNQを使ったデモ4(消費電力)

Jupyter NotebookとPYNQを使ったデモ4(消費電力)