キーワード半導体製造技術を理解するためのキーワード(基礎編)デジタルアドバンテージ 小林 章彦2005/07/30 |

|

|

|

|

2005年7月25日、Intelは米国アリゾナ州チャンドラーの製造拠点に300mmウエハ対応の半導体量産製造施設(Fab 32)を新たに追加、建設すると発表した(インテルのニュースリリース「米国アリゾナ州に300ミリ・ウエハ施設を新設」)。この製造施設では、2007年下半期から45nmプロセスでマイクロプロセッサの製造を開始するとしている。現在、Intelの主力製品であるPentium 4やPentium Mといったプロセッサはすべて90nmプロセスで製造されており、2005年末から2006年にかけて65nmプロセスによるマイクロプロセッサの製造を開始することを明らかにしている。Fab 32は、そのさらに次世代となる45nmプロセスをターゲットにした製造施設である。

このような半導体製造技術の進歩によって、プロセッサの動作クロックの向上や新しい機能の追加が可能になる。また1枚のウエハから製造できるプロセッサ数が増加可能になり、その結果、低価格化も実現できる。そのため、プロセッサ関連の記事には、「xxnmプロセス」や「ダイ・サイズ」といった用語や、トランジスタ数などがよく示される。これらの記事を読むための基礎知識として、半導体製造技術の基本的な用語を解説する。

なぜ0.7倍で微細化されるの?

通常、プロセス・ルールは1年半から2年おきに、1/√2(約0.7倍)ずつ微細化される。これにより、同じ設計のプロセッサであっても、プロセス・ルールだけを変更することで、面積を半分(縦0.7×横0.7=面積0.49)にすることができる。0.8倍程度では微細化によるダイ・サイズ縮小のメリットがあまりなく、逆に0.5倍にもなると製造装置の大幅な改良が必要になり、微細化を実現するための技術的な障害も増えることから、0.7倍に落ち着いているようだ。

Intelでは、Pentium III世代で180nm(0.18μm)から130nm(0.13μm)、Pentium 4世代で130nmから90nm(0.9μm)といった具合に、同一アーキテクチャを採用しながらプロセス・ルールの微細化を実行している。これにより、当初は異なるプロセス・ルールをモデルごと(主に動作クロックが異なる)に使い分け、新しいプロセス・ルールへ徐々に移行することを可能にしている。もちろん、新しいアーキテクチャを最新のプロセス・ルールに最適化する、すなわちアーキテクチャとプロセス・ルールを同時に変更すると、大幅な性能向上が期待できるといったメリットもある。ただ新しいプロセス・ルールは、歩留まり率が向上するまで時間がかかる。そのため、立ち上げ当初はあまり大量には製造できず、製品の安定供給が難しくなるという面がある。そのためIntelでは、新アーテキチャのプロセッサの供給量が需要に応えられなくなるリスクを避けるため、アーキテクチャとプロセス・ルールを同時に変更しないようにしているようだ。具体的には、現行のプロセッサで新しいプロセス・ルールを立ち上げ、その成果を新しいアーキテクチャに適用するという手法を採用している。

| プロセス名 | Px60 | P1262 | P1264 | P1266 | P1268 |

| リソグラフィ | 130nm | 90nm | 65nm | 45nm | 32nm |

| ゲート長 | 70nm | 50nm | 35nm | 25nm | 18nm |

| ウエ・サイズ | 200/300mm | 300mm | 300mm | 300mm | 300mm |

| 製品出荷開始 | 2001年 | 2003年 | 2005年 | 2007年 | 2009年 |

| Intelのプロセス・ルールとゲート長の関係 | |||||

ウエハ・サイズも重要?

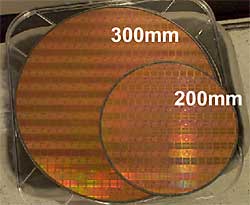

前述のIntelのニュースリリースでも、「300ミリ・ウエハ施設を新設」とタイトルにウエハ・サイズが示されているように、プロセス・ルールとともにウエハ・サイズは製造コストに大きな影響を与える。ウエハ・サイズが大きくなれば、それだけ1枚のウエハから製造できるダイの数は増えることになる。200mmから300mmへの移行で、1枚のウエハで取れるダイの数は約2.5倍になる。一方で製造にかかるコストは、ウエハ・サイズによって大きく上がることはない。ある半導体ベンダによれば、ダイあたりの製造コストは30%低減するとしている。そのため多くの半導体ベンダが直径200mmのウエハ(200mmウエハ)を採用している中、Intelはいち早く300mmウエハの採用を開始している。

|

| 200mmウエハと300mmウエハの違い |

| 直径100mmの違いだが、300mmウエハがかなり大きなことが分かる。これにより同じ製造プロセスならば、2倍以上のダイが取れるようになる。 |

では、300mmといわず、400mm、500mmと大きくすればいいのかというと、話は簡単ではない。まずウエハを製造するためのインゴット(ウエハを切り出す前の円柱型のシリコン結晶)を太く生成するのが難しい。次にウエハの直径が長いと製造過程でウエハ表面の平滑性を維持するのが難しくなり、歩留まりが悪化する危険性がある。さらに製造装置が大型化してしまうなどの問題もある。もちろん、技術が進めば、400mm、500mmといったウエハ・サイズが標準的に利用される日が来ると思われるが、現時点では300mmウエハが経済的で最大のサイズとなっている。

AMDも、ドイツのドレスデンの半導体量産製造施設(Fab 30)に隣接して、300mmウエハ対応の製造施設(Fab 36)を建設中だ。2006年上半期には、Fab 36で65nmプロセスによる量産が開始される予定となっている。この構造施設が完成すれば、製造コストの面でもIntelに対抗できるようになる。AMD Opteron/Athlonの低価格化や、性能面/機能面での強化(2次キャッシュの増量やマルチコア化など)も可能になるだろう。

| 関連リンク | |

| 米国アリゾナ州に300ミリ・ウエハ施設を新設 | |

| 「System Insiderのキーワード」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|