元麻布春男の視点Rambusの次の一手「Yellowstone」の可能性 |

|

米国時間10月22日、Rambusは次世代メモリ・インターフェイスの基礎技術として、「Yellowstone(イエローストーン)」を発表した(Rambusの「Yellowstoneに関するニュースリリース」)。米国最古の国立公園の名前をとったYellowstoneは、次世代メモリを接続するバスの電気信号の仕様に関する技術である。従来のRambusインターフェイスのように、具体的なメモリを接続するための完成されたインターフェイス・パッケージではなく、将来のインターフェイス・パッケージの基盤となるものと考えればよい。ちょうどRambusインターフェイスに対する「Rambus Signaling Level」だと考えればよいだろう。

Yellowstoneはピン当り3.2Gbits/sのデータ転送レートを実現

Yellowstoneの最大の特徴は、下図で示すように外部クロックの8倍(ODR: Octal Data Rage)のデータ・レートをサポートしている点にある。チップ内蔵のPLL回路*1(すでに試作に成功)で外部クロックに対して4倍の周波数の内部クロックを作り出し、さらに内部クロックの立ち上がりと立ち下がりの両エッジに同期させてデータを出力する。外部クロックは、現時点では現行のDirect RDRAM(PC800)と同じ400MHzとされており、ピン当りのデータ・レートは8倍の3.2GHz相当ということになる。

| *1 PLLとはPhase-Locked Loopの略で、位相ロック・ループとも呼ばれる。PLLに入力する信号に対して、周波数を何倍かに高めた出力信号を得られる。PC内部でも、ある基準クロック信号からさまざまな周波数の信号を生成するのに、PLLがよく利用されている。 |

|

| Yellowstoneが採用するODR |

| このようにYellowstoneでは、外部クロックの4倍の内部クロックを作り、その内部信号の立ち上がりと立下がりの両方のエッジを利用して8倍のデータ・レートを実現する。 |

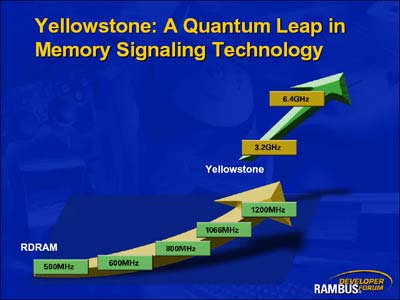

Yellowstoneが、どのようなインターフェイス・パッケージとして提供されるのか不明であるため、最終的なバス幅などが分からないが、現在のDirect RDRAMと同じ16bit幅なら6.4Gbytes/s、以前のRDRAMと同じ8bit幅でも3.2Gbytes/sがそれぞれインターフェイス当りの帯域として実現する。すでにDirect RDRAMでは、外部クロックを400MHzから533MHzに高めたPC1066、同じく600MHzまで高めたPC1200の計画が公表されており、Yellowstoneにおいても同様な措置が可能かもしれない。少なくとも下図のロードマップにおいて、将来的にピン当りのデータ・レートを2倍の6.4GHzに引き上げる構想を持っていることが明らかにされている。

|

| Rambusのロードマップ |

| 時期は未定ながら、PC1200とオーバラップするようにYellowstoneを採用したRDRAMが登場してくるようだ。またYellowstone自体も、3.2GHzから6.4GHzにまで引き上げられる計画があることが分かる。 |

このような高いデータ・レートを実現するために、Yellowstoneでは下図に示すような双方向の差動伝送*2によるインターフェイスを採用した。信号の電圧振幅は、Direct RDRAMが1.0V〜1.8Vの0.8Vに対し、1.0V〜1.2Vの0.2Vと非常に小さい。また、チップ内にターミネータ*3を設けるなどして、信号の乱れを極力排除する。こうした措置により、データ・レートを8倍にするにもかかわらず、現行の4層プリント基板で対応可能、つまり基板などのコストは変わらない、としている。

| *2 差動伝送とは、2本の信号線を駆動することで1つの信号を伝送する方式の一種で、平衡伝送とも呼ばれる。2本の信号線間の電圧(電位差)で、「0」か「1」を決める。1本の信号線で1つの信号を伝える「不平衡伝送」に比べると、ノイズ耐性に優れ、より高速な伝送を可能とする。 |

| *3 ターミネータとは、信号線を伝わる電気信号の波形が乱れるのを防ぐための部品のこと。終端抵抗とも呼ばれる。Rambusなど高速な内部バスのほか、SCSIやISDNのS/T点など、長いケーブルを用いる外部インターフェイスでもターミネータはよく利用される。 |

|

| Yellowstoneの信号 |

| Yellowstoneでは、双方向の差動信号を用いる。その電圧振幅は200mVと小さく、高クロックを意識している(振幅が小さいほど、信号の値を変化させるのに必要な時間が短くなり、クロックを高めやすい傾向があるため)。また、チップ内にターミネータを設けることで、信号の乱れを排除する工夫も加えられた。 |

Yellowstoneに対するIntelの態度

コストはあまり変わらず、性能がPC800に対して4倍になるのであれば、それは結構な話だが、いくつか気になることもある。最も気になるのが、Yellowstoneに対するIntelの態度だ。IntelとRambusは2001年9月に広範なクロスライセンスを締結したばかりだ(Intelの「Rambusとのクロスライセンスに関するニュースリリース」)。しかし、今回のYellowstoneに関するニュースリリースには、Intelの支持表明が含まれていなかった。Rambusは、Yellowstoneベースのメモリ・インターフェイスの用途として、デスクトップPC以外に民生機器やサーバ/ワークステーションを挙げているものの、民生機器以外の分野でIntelが大きな影響力を持っていることはいうまでもない。特にDirect RDRAMベースのPCチップセットを提供しているのが現時点でIntelのみであることを考えればなおさらだ。

YellowstoneについてIntelがどう考えているのか、今のところ知ることはできないが、考えられるのは次の3つの方針だ。

- 基本的にYellowstoneをベースにしたメモリ・インターフェイスを採用する方向にあるが、メモリ・インターフェイスとして完全にパッケージされていない現段階でのコミットは控えている

- 市場の趨勢から、DDR SDRAMのサポートを行わざるを得ないため、Yellowstoneベースのメモリ・インターフェイスについては白紙

- Intelが将来的に考えるメモリ・インターフェイスは、YellowstoneのようなDirect RDRAMの改良型ではなく、完全なシリアル・インターフェイスであるため、Yellowstoneにコミットできない

1.は、これまでIntelがRambusにコミットしてきた延長線上にあり、特に説明を必要としないだろう。2.の方針が考えられる理由の1つは、現在のDRAMベンダ、特にRambusを支持してきた日本のDRAMベンダの置かれた状況にある。東芝は、他社との事業統合によりDRAM事業を本体から分離したい意向にあり、出資比率を連結対象外になる5割以下にしたいといわれていることを考えれば、事実上の撤退、あるいは事業売却にも等しい。つまり、RDRAMを製造していた「Samsung Electronics」「日本電気(エルピーダメモリ)」「東芝」の御三家(?)の1社は消えてなくなる可能性が高い。事業統合後にRDRAMの製造をどうするかは、相手が5割以上の出資比率を持つ以上、パートナー次第、ということになるだろう。

また、東芝と同じく早期からのRambusパートナーである日本電気は、2004年までにDRAM事業を日立製作所との合弁であるエルピーダメモリに全面移管させる計画だが、半導体部門で9000人におよぶ一時帰休に踏み切ることを発表するなど、半導体事業の屋台骨が揺らいでおり、必ずしも見通しは定かではない。Intelは、2002年中ごろにコストを低減したDirect RDRAMのバリエーションである4i(4バンク構成)のDirect RDRAMをサポートした開発コード名「Tulloch(テュロック)」で呼ばれるチップセットをリリースする予定だったが、ここにきて現行のIntel 850のFSBを533MHzに引き上げた、開発コード名「Tehama-E(ティハマ・イー)」で呼ばれるチップセットで対応してしのぐ方針に切り替えたようだ。おそらく4iのDirect RDRAMの供給に不安があるからだろう。少なくとも、Samsung Electronicsの1社しか供給しないDirect RDRAMではサポートできない、という事情だと考えられる。そうなれば、残るのはDDR SDRAMしかない。

3.は、最もアグレッシブな方針だが、Intelが将来、光インターフェイスへの移行を強く示唆していること考えれば、それほど突飛な話ではない。光への前段階として、サイドバンド(データ信号に付随する制御信号など)のない純粋なシリアル・インターフェイスへの移行が1つのステップになると思われる。しかし、クロック信号をデータ信号に多重化しない、つまりクロックとデータをそれぞれ別々の信号線で伝送するYellowstoneが、これに当てはまらないのは明らかだ。

Intelが思うほどメモリ帯域は必要ではない?

どのシナリオが正しいのかが分からないのは前述したとおりだが、さらに話がややこしくなるのは、以上の3つが必ずしも排他の関係にあるとは限らないことだ。たとえば、とりあえず2003年はDDR SDRAMで、2006年あたりにYellowstone、2010年にシリアル・インターフェイスというような、3つのメモリ・インターフェイスがすべて採用されるシナリオですら、考えられないわけではない。要するに、いつ頃にどれくらいの帯域が必要になるか(あるいはIntelはいつ頃にどれくらいの帯域が必要になると考えているか)、という時間の問題を抜きにして、予想することは難しい。

そもそもメモリの帯域については、メモリ・ベンダやIntelがいうほど、必要なものなのか、という疑問がつきまとう。PC133 SDRAMメモリとPC800 RDRAMとの間には、ピーク帯域には1Gbytes/sと1.6Gbytes/s(Intel 850のデュアル・チャネルのPC800では3.2Gbytes/s)と大きな差があるものの、多くのベンチマーク・テストはその差を反映しない。これにはいろいろな理由が考えられると思うが、結局のところ、「一般的なユーザーが使うアプリケーションは、メモリの帯域がボトルネックになるような性質のものではない」ということだろう。これを覆すようなアプリケーション、あるいはユーセージ・モデル(利用方法)が普及しない限り、メモリなんて安ければ安いほどよい、ということになってしまうだろう。となれば、DRAM事業は当面の間、体力勝負の持久戦が続くことになる。![]()

| 関連リンク | |

| Yellowstoneに関するニュースリリース | |

| Rambusとのクロスライセンスに関するニュースリリース |

|

| 「元麻布春男の視点」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|