解説

|

|

|

|

|

Itaniumの継続も強調

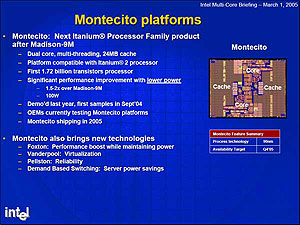

このSmithfield以外にデュアルコア・プロセッサとして2005年内に量産されることが公表されているのが、Itaniumプラットフォーム・ファミリ(IPF)のMontecito(モンテシト)と、そのデュアルプロセッサ版であるMillington(ミリントン)だ。IPFとしては、初めて90nmプロセスで量産され、IA-32のHTテクノロジに相当するマルチスレッド技術を併用することで、1つの物理プロセッサで4つのスレッドを同時実行可能となる。上位のMontecitoについては、コア当り12Mbytes、合計24Mbytesの3次キャッシュを内蔵することが明らかにされており、そのトランジスタ数は17億2000万個にも及ぶ。だが、プロセス微細化の恩恵もあり、消費電力は100Wへと抑えられている。機能的にも、プロセッサが内蔵する温度センサーからのデータで動作クロックを変動(温度に余裕がある場合は必要に応じてオーバークロック動作を行う)させるFoxton(フォックストン)テクノロジ、仮想化技術であるIntel Virtualizationテクノロジ(旧Vanderpoolテクノロジ)、大容量キャッシュメモリの信頼性を確保するPellston(ペリストン)テクノロジなど、さまざまな機能拡張が施されている。

|

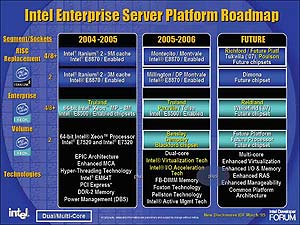

| サーバ・プラットフォームのロードマップ |

| デュアルコア/マルチコア・プロセッサが中核となることが分かる。また2006年以降もIPFに新プロセッサが投入されることが明らかになった。 |

|

| 2005年第4四半期の出荷が予定されるMontecito |

| Smithfieldとは異なり、2つのコアやキャッシュが1つのダイ上で融合しており、当初からデュアルコアを前提に設計されたダイであることがうかがえる。 |

2004年2月のIDF Spring 2004の時点では、Montecito向けに新しく開発コード名「Bayshore(ベイショア)」と呼ぶチップセットがリリースされ、メモリ技術のアップデート、PCI Express対応などが図られることになっていた。ところが、その後キャンセルされてしまった。Montecito自体は、既存のItanium 2とピン互換性を維持しており、そのまま利用することが可能だが、新しいプラットフォーム技術の採用は2007年以降に登場するRichford(リッチフォード)プラットフォームまで持ち越しとなってしまった。Richfordは、Intel Xeon MPとのチップセット共通化が図られることが明らかにされている。

これだけではIPFの将来が暗いと見なされると考えたのか、IntelはTukwila(ツクウィラ)のさらに次の世代のプロセッサとしてPoulson(ポウルソン)という開発コード名を公開している。TukwilaでIntel Xeon MPとのプラットフォームの共通化が行われたら、IPFは収束させて、Intel Xeon MPへの移行が開始されるはず、といううわさを打ち消す意味もあったのかもしれない。

またMontecitoとTukwilaの間にMontvale(モントベール)というプロセッサが存在することも明らかにされた。しかしMontvaleはMontecitoのマイナーチェンジ版だと考えられており、Montecitoを65nmプロセスにシュリンクし、3次キャッシュのさらなる増量などが行われるものと考えられる。

モバイルPC向けにもデュアルコア・プロセッサを投入

話をIA-32プロセッサに戻すと、65nmプロセスによる最初の製品として登場するのは、モバイルPC向けのYonah(ヨナ)だ。現行のPentium 4を2つ並べたようなSmithfieldと異なり、Yonahは最初からデュアルコアのプロセッサとして設計されたものだとされている。従って、動作条件(バッテリ駆動/AC駆動)などにより、機動的に動作モード(シングルコア動作、デュアルコア動作)を変更可能だともいわれている。また、Yonahにはシングルコア版も用意されることになっており、ULV(超低電圧版)やLV(低電圧版)といった消費電力を抑えなければならない製品に採用される可能性が高い。ただ、シングルコア版が最初からシングルコアとして設計されたものになるのか、デュアルコアの片側を無効にしたものになるのかは、現時点では明らかにされていない。なお、YonahではSSE3のサポートに加え、SSE/SSE2の性能向上が図られており、こうしたマルチメディア関連性能の引き上げをIntel Digital Media Boostと名付けている。

|

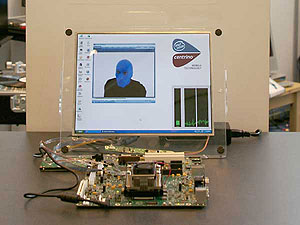

| 会場でデモされていたYonahの評価システム |

YonahのプラットフォームであるNapa(ナパ)は、チップセットのCalistoga(カリストガ)、無線LANモジュールであるGolan(ゴラン)で構成される。PCI Express対応のGolanは、現在使われているMini PCIベースの無線LANモジュールの半分程度の大きさに小型化されている。Banias(バニアス)、Dothan(ドーサン)と電圧レギュレータの仕様(IMVP IV)が同一であったため、ピン互換性を維持することが可能だったが、Napaプラットフォームでは電圧レギュレータの仕様が更新されることが明らかになっていることから、プロセッサのピン互換性は失われる可能性が高い。

65nmプロセス世代のサーバ向けデュアルコア・プロセッサは?

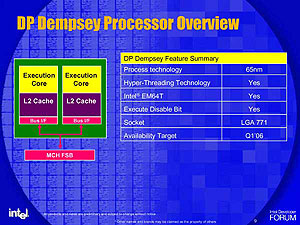

Yonahに続いて65nmプロセスによるデュアルコア・プロセッサとして登場してくるのがサーバ向けのDempsey(デンプシー)と、90nmプロセスによるPaxville(パークスビル)だ。いずれも2006年第1四半期のリリースが予定されている。Paxvilleは、4ウェイ以上のマルチプロセッサに対応しており、1つのダイ上に2つのコアを集積した点ではSmithfieldと同様だが、バス・インターフェイスが1つに統合されている点が異なる。プラットフォームは3月30日に発表されたばかりのTruland(トゥルーランド)を継承しており、次の世代のTulsa(タルサ)プロセッサまで互換性が維持される(インテルのニュースリリース「インテル 64 ビット・エンタープライズ・プラットフォームの製品を拡充」)。ちなみにTrulandは、「64bit Intel Xeon MP」と「Intel E8500」で構成される。

Tulsaの次のプロセッサ「Whitefield(ホワイトフィールド)」は、後述のFB-DIMMに対応したチップセットを用いたReidland(レイドランド)プラットフォームが採用される予定だが、恐らくここでIntel Xeon MPとIPFでプロセッサ・バスの統合が図られる。Itanium 2向けのBayshoreチップセットがキャンセルされた段階で、このプラットフォーム共通化構想がどうなるのか懸念されたが、少なくとも今回のIDFではこの計画に変わりがないことが示された。

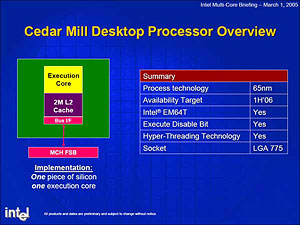

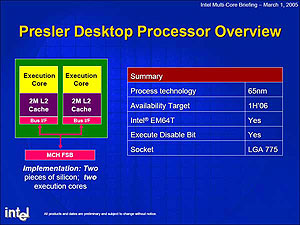

一方、デュアルプロセッサ対応のDempseyだが、現在のデュアルプロセッサ対応Intel Xeonがそうであるように、デスクトップPC向けのPentium Dと高い共通点を持っているものと考えられる。このDempseyに相当するデスクトップPC向けプロセッサはPresler(プレスラー)と呼ばれているが、Dempsey、Preslerともに、1つのプロセッサ・パッケージの中に2つのダイが封入された形となる。しかもデスクトップPC向けには、ダイを1つにしたバージョン(廉価版)が提供されることが明らかになっている。この廉価版は、Cedar Mill(シダー・ミル)という開発コード名が付けられている(Cedar Millについては、「2004 Intel fall Analyst Meeting」で公表済み)。

同じコアを異なるターゲット向けに味付けを変えて投入

Intelでは、1つのプロセッサ・パッケージの中に、独立した実行コアを2つ内蔵したものを「デュアルコア」と呼んでおり、ダイの数とは無関係だという。ダイの数をどうするかは、もっぱらデザイン効率や経済効率により決定され、ダイの数の違いによってOEMやユーザーが影響を受けることはないとしている。もっともなようにも思う一方で、それならもっと早期にデュアルコア化が可能だったのではないかとも思う。

Cedar Mill、Presler、Dempseyは、ほぼ同じコア(ダイ)を、1つ封入したデスクトップPC向け、2つ封入したデスクトップPC向け、2つ封入したデュアルプロセッサ対応サーバ向け、という関係にあり、一種の三つ子プロセッサともいえる。封入されるダイの仕様は若干異なり、Cedar MillではHTテクノロジが有効(1コア2論理プロセッサ)、PreslerではHTテクノロジが無効(2コア2論理プロセッサ)、DempseyではHTテクノロジが有効(2コア4論理プロセッサ)となる。

|

|

|

| 65nmプロセスによる三つ子プロセッサ |

| 基本的なコア構成は同じだ。Cedar Mill(上)は、Presler(中)やDempsey(下)で採用されるコアの片側のみを実装する。PreslerとDempseyの主な違いは、ユニプロセッサ向けかデュアルプロセッサ向けかと、ソケットの種類になる。 |

今回の説明にはなかったが、Preslerの時点で、HTテクノロジを有効にしたPresler XEがPentium Extreme Edition用に提供される可能性は高いのではないかと思う。DempseyとPresler XEは、コア的にはほぼ同等のスペックだが、パッケージ(ソケット)が異なり、プラットフォームが違う、という関係になる。また、Cedar Millは(少なくとも当初は)Pentiumブランドのプロセッサとして提供されることも明らかにされた。つまり、Pentium Dプロセッサでプロセッサ・ナンバーが小さいものにCedar Mill、大きいものにPreslerが使われる見込みだ。将来的にはCedar MillはCeleronブランドのプロセッサにも使われるのだろうが、そのときはHTテクノロジが無効にされるかもしれない。

Preslerを用いたプラットフォームについては、企業クライアント向けがAverill(出荷当初は既存のLyndon)、ホーム・クライアント向けがBridge Creek(同Anchor Creek)とそれぞれ開発コード名が明らかにされたが、中身から考えてCedar Millも同じプラットフォームが使えるだろう。チップセットの開発コード名としては、Broadwater(ブロードウォーター)しか公開されていないが、Extreme Edition向けのチップセットもラインアップされるだろう。また、この2つのプラットフォームは、どうやら次の世代のプロセッサ「Conroe(コンロー)」にも継承されるようだ。それぞれのプラットフォームの内容についてはほとんど説明されていないが、メモリ・ロードマップのセッションの説明から考えると、メモリ・クロックが引き上げられ、DDR2-800がサポートされる可能性が高い。また、iAMTが2世代目に入り、これに対応したギガビット・イーサネット・チップ(開発コード名:Nineveh)が採用される見込みだ。

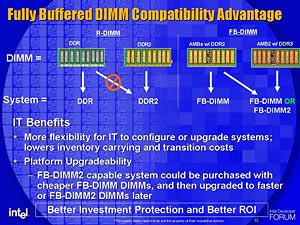

一方、Dempseyのプラットフォームとしては、サーバ向けにBensley、ワークステーション向けにGlidewell、2つが用意される。Bensleyの中核となるチップセットはBlackfordで、初のFB-DIMM(Fully Buffered DIMM)対応チップセットとなる。FB-DIMMは、DIMM基板上にAMB(Advanced Memory Buffer)と呼ばれるインターフェイス・チップを搭載することで、AMBとチップセット間をPCI Expressをベースにしたシリアル・インターフェイスで接続する。多数のチップを接続するのに不適なDRAMのパラレル・インターフェイスをDIMM基板上(AMBチップとDRAMチップ間)に限定することで、より大容量のメモリの搭載が容易になる。

|

| FB-DIMMのメリット |

| FB-DIMMではAMBとチップセット間のインターフェイスが一定であるため、DDR2メモリを用いたFB-DIMMからDDR3メモリを用いたFB-DIMM2への移行も容易になる。 |

|

| 基調講演でFB-DIMMを手にするパット・ゲルシンガー新事業部長 |

| DIMM中央のチップがAMBと呼ばれるインターフェイス・チップである。 |

また、チップセット側のインターフェイスとメモリ・デバイス側のインターフェイスが分離されるため、AMBチップを交換することにより、1つのチップセットで複数世代のDRAMに対応することが可能になる。実際には電源電圧のサポートなどの点から、すべてのシステム/マザーボードが複数世代のDRAMに対応するとは限らないが、現在DDRとDDR2を同じチップセットでサポートするよりも容易に、異なる世代のDRAM(例えばDDR2メモリとDDR3メモリ)をサポートすることが可能になるだろう。なお今回のIDFでは、DDR2メモリを用いたFB-DIMMのデモンストレーションが行われた。

マルチコア化は有効なのか?

IDFで公開された主要な開発コード名についてはおおむね以上のようなものだが、最も根本的な疑問として残るのは、プロセッサのデュアルコア化、マルチコア化は本当に有効なのか、ということだ。もちろん、すでにマルチプロセッサ・システムが一般的なサーバ分野に関しては、この疑問は存在しない。デュアルコアやマルチコアのプロセッサを搭載したサーバは、最初から高い性能を示すだろう。ちなみに、現在、暫定の最高技術責任者(CTO)を勤めるジャスティン・ラトナー(Justin R. Rattner)シニア・フェローに、「将来マルチコア・プロセッサは、マルチプロセッサ・システムを置き換えることになるのか」という質問をしてみた。氏の答えは、完全に置き換えることはないかもしれないが、ハイエンドでも8ウェイ(物理プロセッサが8個)くらいの構成になるのではないか、というものだった。

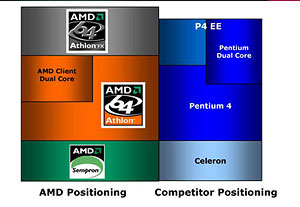

サーバにおいてデュアルコア/マルチコア・プロセッサが有効なのは、すでに主要ソフトウェアにおけるマルチプロセッサ構成への対応が進んでいると同時に、一般的なサーバの用途は非同期のトランザクション処理が中心で、そもそもプロセッサの多重化と相性がよいという理由がある。逆に、コンソールの前のユーザーによるインタラクティブな操作が主で、アプリケーションのマルチスレッド化が必ずしも進んでいるとはいえないクライアントPCの場合、動作クロックの高いシングルコア・プロセッサに対してどれくらい性能的なアドバンテージがあるのかは疑問が残る。実際、同じようにプロセッサのデュアルコア化を進めているライバルのAMDは、当初はデュアルコア・プロセッサをハイエンド・クライアント向け(Athlon 64-FX)にポジショニングしない。これはAthlon 64-FXの顧客が利用するアプリケーション(ゲーム)の大半がシングルスレッドであるからだという。

|

| AMDによるデュアルコア・プロセッサの位置付け(クライアントPC) |

| この図を見ると分かるようにAMDでは、ハイエンド向けのAthlon 64-FXにはデュアルコアを適用しない。これは主にAthlon 64-FXが対象とするユーザーのアプリケーション(ゲーム)がシングルスレッド中心であるためだ。 |

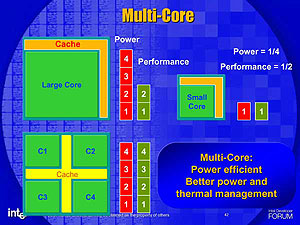

プロセッサをマルチコア化する大きなメリットは、消費電力当たりの性能を向上できること、プロセッサ上のホットスポット(熱上昇領域)を分散できることにある。こうしたメリットは、ユーザー・メリットというよりも、作り手側のメリットに近い。ソフトウェアの対応により、デュアルコア/マルチコアをユーザーのメリットに結びつけることができるかどうか、あるいはそれがどれくらいのスピードで可能なのかが、今後問われることになるだろう。![]()

|

| Intelが示したマルチコア化のメリット |

| Intelでは、マルチコア化によって、消費電力当たりの性能を向上できることをメリットとして挙げている。さしずめ「Large Core」はキャンセルになったTejas/Jayhawkとなるのだろう。 |

| INDEX | ||

| [解説]IDF Spring 2005から読み解くIntelのプロセッサ戦略 | ||

| 1.デュアルコアへと大きく舵を切ったIntel | ||

| 2.デュアルコア/マルチコアを中心に展開されるサーバ向けプロセッサ | ||

| 「System Insiderの解説」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|