解説IDF 2007, Beijingレポート

|

|

大きく変わるプラットフォーム

すでに述べたように5種類に及ぶPenrynファミリのプロセッサは、現行のCoreマイクロアーキテクチャを継承した製品であり、基本的にピン互換性を持たせることができる。これを踏まえて、次世代のプラットフォームをまず現行のプロセッサで立ち上げ、そのプラットフォームを45nmプロセス製造のプロセッサに引き継ぐことで、新プラットフォーム立ち上げ時にトラブルが生じるリスクを軽減する、というのも従来からのIntelの戦略だ。

■いち早く次世代プラットフォームが提供されるモバイル向け

この中で次世代プラットフォームの立ち上げが、最も早期に予定されているのがモバイルPCの分野だ。現行のNapa(ナパ)プラットフォームはもともとCore Duoプロセッサ(Yonah:ヨナ)でスタートし、Core 2 Duoプロセッサ(Merom:メロム)へと引き継がれた。次のプラットフォームであるSanta Rosa(サンタ・ローザ)はMeromでスタートし、Penrynへ引き継がれるというわけだ。

Santa Rosaプラットフォームの中核となるのは、すでにデスクトップPC用に展開されているIntel 965チップセットをベースに、モバイル向けに改良したGM/PM/GL965チップセット(Cresline:クレスライン)となる。Windows Vista上の動画品質を向上させるIntel Clear Video Technology、リモート管理機能「iAMT(Intel Active Management Technology) 2.5」に対応可能な無線LANモジュールであるIntel 4965AG/4965AGN(Kedron:ケドン)で構成される。Intel 4965AGNの末尾のNは、IEEE 802.11nのドラフトに準拠していることを示し、既存の無線LANに対し最大5倍(40MHzチャンネルオプション利用時。国内でのサポート時期は未定)のデータ転送速度が実現される。さらにSanta Rosaのオプションとして、NANDフラッシュメモリを用いたディスク・キャッシュ技術であるIntel Turbo Memoryの提供も行われる。

次のMontevina(モンテヴィーナ)プラットフォームでは無線MAN技術であるWiMAXの統合や、Intel Turbo Memoryの改良が明らかにされているほか、DDR3メモリへの対応が行われる見込みだ。動作電圧がDDR2の1.8Vから1.5Vへ引き下げられるDDR3メモリは、デスクトップPC以上に、消費電力や性能の面でモバイルPCにメリットがあるといわれている。

Santa Rosaプラットフォームからわずかに遅れて登場すると見られるのが、新たに提供されるIntel 3シリーズのチップセットだ。これまでBealake(ベアレイク)という開発コード名で知られてきたIntel 3シリーズのチップセットは、バリュー・セグメントからハイエンドまで、あるいはコンシューマ向けとビジネス向けといったセグメントごとに、合計7種類のバリエーションが展開されることになっている。コンシューマ向けのグラフィックス統合型がG31/G33/G35、ビジネス向けのグラフィックス統合型がQ33/Q35、外付けグラフィックスを利用するP35、ハイエンド向けのX38というラインアップだ。

|

| Intel 3シリーズ・チップセットのラインアップ |

| 合計7種類がラインアップされるIntel 3シリーズのチップセット。最もローコストなG31を含め、すべてのチップセットでクワッドコア・プロセッサ対応となる。 |

プラットフォームとしては、ビジネス向けがWeybridge(ウェイブリッジ)、コンシューマ向けがSalt Creek(ソフト・クリーク)と呼ばれ、それぞれvPro、Viivのブランドで提供されることになる。これらはそれぞれの上位チップセットを用いたものだが、もちろん下位のチップセットを用いたプラットフォームも用意される)。従来の例にならって、このBearlakeがベースとなって、上述のMontevinaプラットフォーム用のチップセット(Cantiga:カンティーガ)が作られることになるだろう。

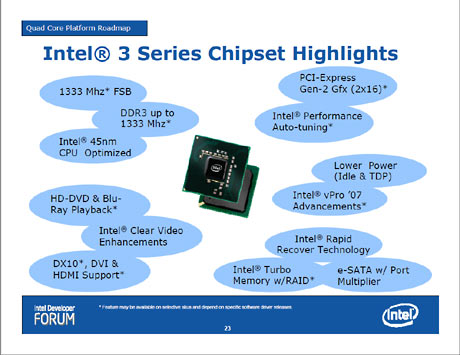

Intel 3シリーズのチップセットがサポートする主要な機能は、下図のとおりである。DDR3メモリのサポート、グラフィックス用にデータレートを2倍の5Gbit/sへ引き上げた第2世代PCI Expressのサポート(16レーンを最大2スロット)、DirectX 10対応のグラフィックス、VT-dのサポートなどが行われる。ただし、すべての製品が、この図中の機能をすべてサポートするわけではなく、それぞれの製品が対応するセグメントに応じて機能を備えることになる。また、リリース時期も7種類が一斉に登場するのではなく、一部は第3四半期にデビューすることになっている。

|

| Intel 3シリーズ・チップセットの概要 |

| すべての機能が、製品に網羅的に採用されるわけではない。 |

■デュアルプロセッサ向けに2種類のプラットフォームが提供されるサーバ向け

一方、サーバ向けのプラットフォームはすべて2007年後半に登場するが、大きな特徴はデュアルプロセッサ(DP)対応のプラットフォームが2種類提供されることだ。いずれも45nmプロセスのプロセッサ(Wolfdale-DPおよびHarpertown)に加え、現行のIntel Xeon 5100シリーズ(Woodcrest:ウッドクレスト)ならびにIntel Xeon 5300シリーズ(Clovertown:クローバータウン)に対応している。そのため、まずWoodcrest/Clovertownでプラットフォームを立ち上げ、45nmプロセス製造へと移行するものと思われる。

2種類のDPプラットフォームは、上位版のStoakley(ストークレイ)と下位版のCranberry Lake(クランベリー・レーク)に分かれる。現在主力となっているBensley(ベンスレイ)プラットフォームの後継と目されるStoakleyプラットフォームは、Seaburg(シーバーグ)チップセットを中核としたものだ。FB-DIMMサポートやエンタープライズ向けICH(サウスブリッジ)のサポートなど、Bensleyプラットフォームを継承しつつ、I/Oの仮想化支援機能であるVT-dのサポート、第2世代PCI Expressのサポート、Intel IOAT2(I/O Acceleration Technology:ネットワーク高速化技術)のサポートなどの強化が図られる。

|

| デュアルプロセッサ対応の上位プラットフォームとなるStoakley |

| FB-DIMMのサポート、エンタープライズ向けICHのサポートなど、Bensleyプラットフォームの直系と考えられる。 |

FSBの動作クロックとして新たに1600MHzをサポートするほか、最大メモリ搭載量はBensleyの2倍の128Gbytesへ拡張される。これにともない、チップセットの物理アドレス空間が36bitから38bitへと拡張される。さらにチップセット側にキャッシュ・タグ情報を持つことでキャッシュ・スヌープ動作によるFSBの帯域占有を軽減するスヌープ・フィルタも、24Mbytesへと増量される。レーン数の構成を柔軟に変更できるPCI Expressの特徴を生かし、Stoakleyプラットフォームは、DPサーバとDPワークステーションの両方に用いられることになる。また、このStoakleyプラットフォームをベースに、ハイエンド向けのハイエンド・コンシューマ・プラットフォームとしてSkulltrail(スカルトレイル)を提供することも予定されている。

これに対してCranberry Lakeプラットフォームは、バリュー・セグメントのサーバや、ブレード・サーバなど高密度サーバ向けのプラットフォームだ。最大の違いはサポートするメモリがFB-DIMMではなく、通常のDDR2メモリになることにある。DDR2メモリの採用は、熱とコストの両面で有利だが、最大メモリ搭載量では不利に働く。ICHもデスクトップPCと同じICH9Rのサポートで、ここでもコストが優先されているのが見て取れる。

|

| デュアルプロセッサ対応の下位プラットフォームとなるCranberry Lake |

| 熱とコストの両面で有利なDDR2メモリをサポートするほか、ICHもクライアント向けチップセットと共通のICH9Rを用いる。 |

現行のIntel 5000チップセットも上位版のIntel 5000X(Blackford:ブラックフォード)チップセットと、下位版のIntel 5000P/V/Z(Blackford-VS)チップセットの2種類で構成されるが、基本的に両者は似通っており、StoakleyとCranberry Lakeほどの違いはない。こうした差異化が今後も続けられるのか、注目されるところだ。

こうしたDPサーバの展開に加え、2007年はいよいよマルチプロセッサ(MP)・サーバが大きく動く。最大4プロセッサをサポートするMPプラットフォームは、IA-32プラットフォーム中、現時点で唯一NetBurstマイクロアーキテクチャが残る分野だ。ようやく2007年第3四半期に待望のCoreマイクロアーキテクチャへの切り替えが行われる。

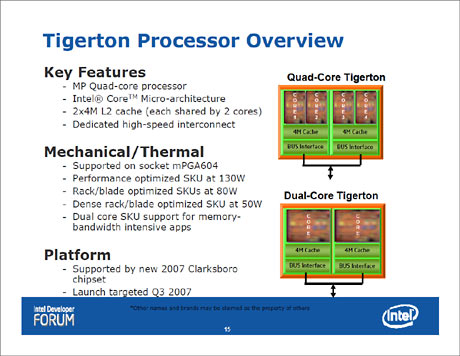

プロセッサはこれまでTigerton(タイガートン)の開発コード名で知られてきたもので、クワッドコア版がIntel Xeon 7300シリーズとなる。DP版同様、4Mbytesの共有2次キャッシュを持つデュアルコアのダイを2枚封入したプロセッサだ。今回のIDFでは、このクワッドコア版に加え、デュアルコア版(Dual-Core Tigerton)もリリースされることが明らかにされた。ただし、このデュアルコア版は、クワッドコアのダイを1枚に減らしたものではない。4Mbytesの2次キャッシュを持つシングルコアのダイ(デュアルコアの片方を無効にしたものとも考えられる)を2枚封入したもので、メモリ帯域に依存したアプリケーション向けの製品だということだ。恐らくハイパフォーマンス・コンピューティング(HPC)のような特定分野に向けたものだと思われる。

|

| 次世代のMPサーバ向けプロセッサ「Tigerton」の概要 |

| TigertonでMPサーバ向けプロセッサもCoreマイクロアーキテクチャへと切り替わる。 |

Tigertonプロセッサのプラットフォームとして用意されるのがCaneland(ケインラン)で、Clarksboro(クラークスボロ)チップセットを中核とするプラットフォームだ。FB-DIMMをサポートし、最大で256Gbytesのメモリを搭載できる。これに合わせて64Mbytesの大容量スヌープ・フィルタを搭載する。

| INDEX | ||

| [解説]IDF 2007, Beijingレポート IntelがIDFで見せた次世代プラットフォーム | ||

| 1.2007年に45nmプロセス製造への移行を開始するIntel | ||

| 2.見ててきたIntelの次世代プラットフォームの姿 | ||

| 3.次世代マイクロアーキテクチャは2008年に登場予定 | ||

| 「System Insiderの解説」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|