単一ダイで3つのアーキテクチャのメモリを実現

Spansion、NOR型の弱点を克服した携帯端末用メモリを発表

2007/04/04

米Spansion代表取締役社長兼CEO バートランド・カンブー(Bertrand Cambou)氏

米Spansion代表取締役社長兼CEO バートランド・カンブー(Bertrand Cambou)氏Spansion Japanは4月4日、異なるメモリアーキテクチャを単一のダイ上に集積できる「MirrorBit Eclipseアーキテクチャ」を発表した。プログラム実行用のメモリとマルチメディアデータなど大容量のデータの保存用のメモリを、実装上区別する必要がなく、携帯電話端末などで「部品単価を30%以上削減できる」(米Spansion代表取締役社長兼CEO バートランド・カンブー氏)。

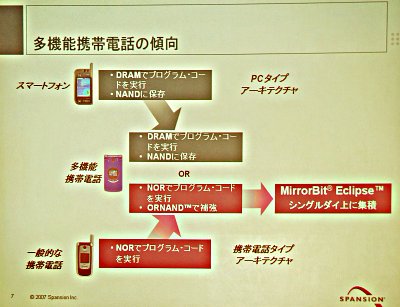

スマートフォンを含むマルチメディア端末の多くは、搭載メモリモジュールとしてプログラムの実行用にDRAM、データ保存用にNAND型フラッシュメモリという構成を取る。これはDRAM+ハードディスクというPCに似たアーキテクチャだ。

一方、NAND型フラッシュメモリよりもランダムアクセスが高速なNOR型フラッシュメモリは、コストや実装面積の点でNAND型に劣るとされてきた。Spansionはこれまでに、NOR型フラッシュメモリで1セル当たりの容量を2ビット、4ビットと多値化すること成功しており、NOR型の弱点を補完する技術を蓄積してきた。今回の発表は、これらの異なるアーキテクチャのメモリを同一のチップ上で使えるようにする技術で、「(アクセスは速いが大容量化に向かないという)NOR型フラッシュメモリのイメージを変えたい。その第1弾がMirrorBit Eclipse」(Spansion Japan代表取締役社長 田口眞男氏)という。

MirrorBit Eclipseの位置付け。DRAMを使わずにコストダウンを図るメインストリーム向け端末市場を狙う

MirrorBit Eclipseの位置付け。DRAMを使わずにコストダウンを図るメインストリーム向け端末市場を狙う組み合わせ可能なメモリの種類は、(1)読み出し速度に優れ、プログラム実行に適したNOR型フラッシュメモリ「MirrorBit NOR」、(2)書き込み速度が速く大容量化の容易なORNAND型フラッシュメモリ、「MirrorBit ORNAND」、(3)読み出し速度は遅いが、1セル当たり4ビットの容量を持つ「MirrorBit Quad」の3種類。これらのメモリアーキテクチャは「MirrorBitアレイと呼ばれる均一なダイで実現しており、まったく同一の製造ラインで生産されている。それぞれのアーキテクチャは、セルをどう使うかで決まる」(カンブー氏)。各メモリの容量の比率はダイに搭載したコントローラで設定できる。

Spansion Eclipseの出荷は2007年第3四半期を予定しており、当初は65nmのチップで、MirrorBit Quadを除くアーキテクチャをサポートする。2008年末までに45nmのプロセスルールに移行し、MirrorBit Quadまで対応する第2世代のチップを出荷予定。

ガンブー氏によれば、スマートフォン市場では今後も一定の割合でDRAMが使われていくが、高機能化が進むメインストリーム向けの多機能携帯電話端末では「MirrorBit Eclipseは2010年までに約60%の市場に対応できる」としている。

Spansionは米AMDと富士通が共同で設立したベンチャー企業で、2006年はNOR型フラッシュメモリ市場でトップシェアを獲得している。

関連リンク

情報をお寄せください:

最新記事

|

|