第230回 AMD Ryzenが高コストパフォーマンスを実現した3つの理由:頭脳放談

久しぶりにAMDのCPUに注目が集まっている。第3世代のAMD Ryzenが性能の高い上に、価格がリーズナブルであると、特に自作PCユーザーに人気だ。AMD Ryzenが高コストパフォーマンスを実現できた理由を考えてみた。

ご存じの方も多いと思うが、このところAMDのCPUの人気がうなぎ登りだ。直近では、第3世代「Ryzen(ライゼン)」 に注目が集まっている。マイクロアーキテクチャ的には「Zen(ゼン)」アーキテクチャの改良版「Zen2」を採用した機種なのだが、「安い上にIntel製CPUよりも高性能である」と、評価が高い。

第3世代AMD Ryzenのイメージビデオ

AMDが公開している第3世代AMD Ryzenのイメージビデオの一部。Ryzenの内部は、3つのチップで構成されているようだ(「第3世代AMD Ryzenテクノロジー」のプレゼンテーションビデオより)。

少し前までは、「AMDって何?」みたいな扱いだったのを覚えているだろうか。秋葉原辺りでは、夜の販売開始でショップに人だかりができたというのだから様変わりだ。しかしこの人気、第3世代Ryzenの新発売で突発的に発生したわけでもなく、また日本だけの傾向でもないようだ。

秋葉原でマザーボードやCPUを買ってPCを組み立てるようなユーザー層(多くは「PCゲーマー」だと筆者は勝手に想像しているのだが)を相手にしたCPUの小売りビジネスでは、第3世代Ryzenを待たずして、シェアでIntel製CPUを逆転していたようだ。

このままの勢いで市場が動けば、いずれビジネス向けの大手メーカー製PCでもそうなる可能性がある。そうなれば、Intelの屋台骨を揺るがすような事態となろう。これが2018年からのIntelのデリバリー(供給)の問題のみに起因しているのであれば、一種のオウンゴールであり、Intelにすればそれを改善すれば反撃できる話である(Intelの供給不足に関する問題は、頭脳放談「第225回 なぜ『IntelのCPU不足』はなかなか解決されないのか?」参照のこと)。

AMDがIntelより優れている3つの理由

しかし、状況を見るにそうではないようだ。「コスパ」という最も基本的な点で、IntelはAMDに負けているのだ。そうなった理由を考えよう。月並みな結論だが3つにまとめられるのではないか、と考えている。

| 製品名 | CPUコア数 | スレッド数 | 最大ブーストクロック | 基本クロック | TDP | L2+L3キャッシュ(MB) | グラフィックス機能 |

|---|---|---|---|---|---|---|---|

| Ryzen 9 3950X | 16 | 32 | 4.7GHz | 3.5GHz | 105W | 72 | − |

| Ryzen 9 3900X | 12 | 24 | 4.6GHz | 3.8GHz | 105W | 70 | − |

| Ryzen 7 3800X | 8 | 16 | 4.5GHz | 3.9GHz | 105W | 36 | − |

| Ryzen 7 3700X | 8 | 16 | 4.4GHz | 3.6GHz | 65W | 36 | − |

| Ryzen 5 3600X | 6 | 12 | 4.4GHz | 3.8GHz | 95W | 35 | − |

| Ryzen 5 3600 | 6 | 12 | 4.2GHz | 3.6GHz | 65W | 35 | − |

| Ryzen 5 3400G | 4 | 8 | 4.2GHz | 3.7GHz | 65W | 6 | Radeon RX Vega 11(1400 MHz) |

| Ryzen 3 3200G | 4 | 4 | 4GHz | 3.6GHz | 65W | 6 | Radeon Vega 8(1250 MHz) |

| Ryzenのラインアップ | |||||||

第1は、いろいろ言われている通り、Zen2マイクロアーキテクチャが「性能のよいもの」だった、という素直な称賛だ。

第2は、製造プロセスだ。Intelに先んじて7nmでCPUコアを作って投入できたことである。製造は、TSMCの7nmプロセスで行われているという。これまで、AMDの製造はGLOBALFOUNDRIES(グローバルファンダリーズ)が担当してきたが、同社は7nmプロセスから脱落している(GLOBALFOUNDRIESのプレスリリース「GLOBALFOUNDRIES Reshapes Technology Portfolio to Intensify Focus on Growing Demand for Differentiated Offerings」)。AMDが、製造先をTSMCに変更したのはよい決断だったといえそうだ。

第3は、マルチダイのパッケージングの採用である。複数個のCPUコアチップと、周辺インタフェースをワンパッケージ化したとのことだ。この辺の理由はAMDの発表通りであるのだが、そこを少しうがって考えてみたい。

Zen2マイクロアーキテクチャの優れた点

第1のマイクロアーキテクチャだが、Zen2になって突然「よくなった」わけではない。Zenのときから「下地はできていた」というべきであろう。それは、市場受けは大変悪かったが、その前の世代の「Bulldozer(ブルドーザー)」が「AMDのターゲット市場とズレていた」おかげで、Zenのターゲットが明確になったというべきじゃないかと思っている。

Bulldozerは言われている程悪いものじゃないように思う。けれど、x86市場の中でAMDが占めていたポジションを考えると「外してしまった」感が強い。結局、AMDのお客は、「1個1個のコアでIntelコアを打ち負かせる」ようなコアを求めていたのであって、HPC向けのコアを求めていたわけでもない。また、Armのお客のように「1個1個のコアではIntelコアには太刀打ちできないが、システムとしてはコスパで上回る」ようなものを求めているわけでもなかった、ということだ。

Zenでは、「コア単体性能」でIntelに勝てることを目標にしたはずであり、このBulldozerからZenへの方針転換の路線上に、Zen2への改良があった(もっと言えばこの先のZen3もあって)というべきだろう。

しかし、方針転換すればそれが簡単に実現できた、などということはあり得ない。このクラスのモダンなプロセッサでは、コア単独性能のほんの数%のアップであっても、その実現のためには膨大な量のトランジスタ(端的に言えばSRAM類似構造のメモリ類の占める割合がとても多いと思う)を必要とする。

ある意味、シングルコアの性能向上のためには「不健全な」までのトランジスタ量が必要とされるのだ。トランジスタ数当たりの性能を考えれば、GPUのように非力な小人を大量に並べる方が効率的で健全といえる。

7nmで先んじた点

巨大な力を発揮する「巨人」を作ろうとしたとき、最も効いてくるのがプロセスなのだ。小さくなればなるほど使えるトランジスタ数は増える。7nmを使えたAMDが、いまだに14nmで「出荷数量に苦しんでいる」Intelに一歩先んじているのは、ある意味当然といえるかもしれない。第2の理由が第1の理由を支えているのだ。

しかし、7nmプロセスが万能かといえば、そうではなかったはずだ。実際、CPUコアモジュールは7nmだが、主に外部とのインタフェースを担う部分は14nmプロセスだ。これを1個のマルチチップ(マルチダイ)モジュールに封止している。内輪の事情をAMDがどこまで公開しているのかは知らない。しかし、この組み合わせは市場への投入時期とコストを熟考した上での判断だったに違いない。

あるロジック用のプロセスを立ち上げるとき、内部のロジック用のトランジスタ、そしてキャッシュなどに使われるSRAM系統のメモリ類は多分最初に使えるようにする。これらがあればCPUチップは作れる。しかし、外部とのインタフェースを担う部分は電気的な特性の縛りが大きい。ある意味アナログ的な開発で設計や検証に時間がかかるはずだ。すると、あるプロセス上で各種回路が使えるようになるまでには時間差ができる。

マルチチップモジュールによるイールドの向上

ここで、シングルチップ(シングルダイ)の製品であれば全てを待たねばならない。一方、マルチチップモジュールであれば、異なるプロセスのチップを混載して結合できる。全部を待つ必要はないわけだ。それに、アナログ的な回路は線幅が小さくなったからといってそのままダイまで小さくなるわけではない。そのため幅広のプロセスで十分ということもあり得る。第3の理由が生きてくる。

マルチチップモジュール自体はふた昔以上前から量産されてきた。けれど、この手の先端、高速なプロセッサ向けに、高速性を殺さず市場価格に見合ったコストでできるようになったのはGPUのおかげだったのではないか、と思っている。先行したのはGPUチップとHBMなどの超高速DRAMの混載だったからだ。この場合、ロジックプロセスのGPUとDRAMプロセスのHBMではワンチップにしようがない(DRAM混載用のプロセスというのもあるのだが、この手の高速プロセッサに使えるような代物ではない)ので、マルチチップ化は必然だった。もちろん、AMDはGPUメーカーでもあり、この手のモジュールに経験がある。その経験と使用実績が大きかったのではないかと想像する。

その上、1個のチップではなく、複数個のチップで製品を構成できるとした場合、コスト上大きなメリットを得られる可能性が高い。今回の第3世代Ryzenの場合、基本は4コア8スレッドをCPUモジュールとして1個のチップにしているようだ。

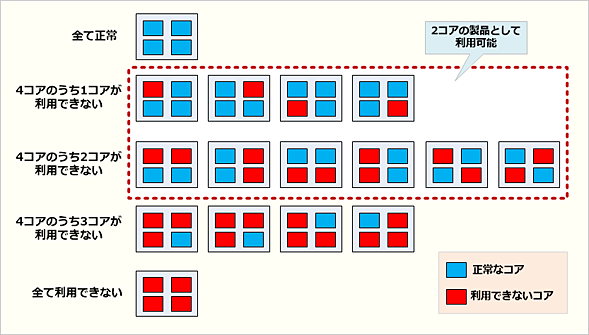

8コア16スレッドの場合は4コア8スレッド×2の構成だが、12コア24スレッドの場合は4コア8スレッド×2+2コア4スレッド×2という構成のようだ。実際のところ、AMDの製造がどうしているのかは知らない。しかし、イールド(収率)が気になる筆者が思うに、全て「ヘルシー」な4コア8スレッドのチップだけでなく、1コア死んでいるチップも、2コア死んでいるチップも「売り物にできるじゃん!」と喜んでしまう。

イールドというのは、ロシアンルーレットのようなものだ。仮に1コアに弾丸が発射される(製品として使えない)確率が50%としよう(実際にそんなに大きかったら大問題だが)。4コア全てがヘルシーになるのは「2の4乗分の1(16分の1)」でしかない。つまり、16個の製品のうち、使えるのは1個、残りは捨てることになる。

しかし、3コアヘルシーでいいのであればさらに4個、2コアヘルシーなら6個取れる。他に1コアヘルシーが4個、全滅は1個だ。もし3コアのものと2コアのものを、2コアとして「お色直し」して使えたとすると、捨てるのは5個で済む。残りの11個は製品として利用できるわけだ。おお、何と経済的なことか!

イールドのイメージ

一定の確率でコアには不良が発生する。4コア全てが正常でなければ製品にできないとなると、イールドは大きく下がってしまう。しかし、少なくとも2コアが正常であれば十分とするなら、イールドは大きく上がる。

そして、チップは小さくすればするほどイールドは急激によくなるのだ(先ほどのロシアンルーレットの死ぬ確率が急激に下がる)。巨大な1個のチップを作るより、複数個のチップに分けられるのであれば、イールドの計算上はコスト効率がよいに決まっている。

ただ、マザーボードの基板の上で複数個のパッケージに分けてしまうと、シングルパッケージと比べて大幅に性能が下がってしまうし、また、その他のコストもかさみ過ぎるので、そうは問屋が卸さなかっただけなのだ。このマルチチップ(マルチダイ)の技術こそ、「コスパ」を支える最重要技術ではないか、と見る。

当然、Intelも新しいプロセス、新しいパッケージング技術で、新しいコアを投入してくるだろう。今度は迎え撃つ立場となるAMD、ここでしのぎきれれば大勝利だが……。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

更新履歴

【2019/07/23】AMD Ryzenの製造は「TSMCの7nm+ EUVプロセス」としておりましたが、「7nmプロセス」の誤りでした。記事を修正しました。

【2019/07/22】初版公開。

Copyright© Digital Advantage Corp. All Rights Reserved.