第262回 パッケージの中で複数のチップを接続する新標準規格「UCIe」はSoCを変える?:頭脳放談

IntelやAMDなどが、パッケージ内で複数のチップを接続するための標準規格「UCIe」を策定するという。異なるプロセスや製造元で製造されたダイを組み合わせてシステムが作れるようになる。今後、10年のパッケージ内のインターコネクトとなりそうだ。

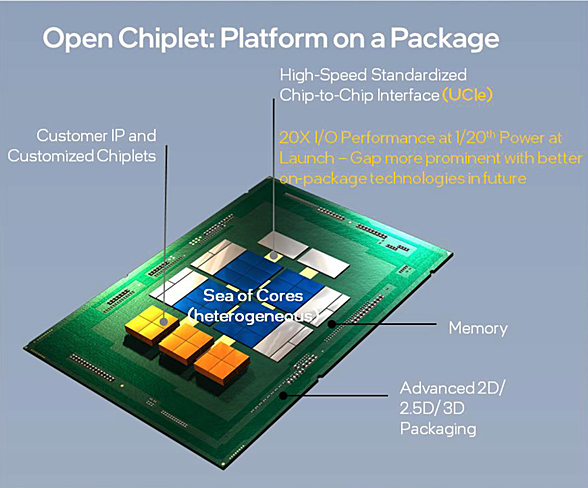

UCIeを採用したパッケージのイメージ

UCIeを採用した複数のダイをパッケージ内で接続できる。異なる製造元のメモリやカスタムしたチップセットであっても、UCIeを採用していれば接続できる。図は、UCIeのホワイトペーパー「Universal Chiplet Interconnect Express (UCIe):Building an Open Chiplet Ecosystem[PDF]」より。

また新たな標準化団体「UCIe(Universal Chiplet Interconnect Express)」が立ち上がった。ざっくりいえば、1つのパッケージ内に複数のダイ(シリコンチップ)を集積して製品を作るための接続規格だ。

昔からワンパッケージ内に複数のダイを集積することは、省スペースを狙いにして携帯電話の普及以来行われてきたことだが、基本アドホック(その場限り)なものであった。

しかし、UCIeは、異なるプロセス、異なる製造元の規格化されたダイを組み合わせて、どちらかといえば高速高機能のハイエンドなシステムを作れる方向性に見える。サーバやスーパーコンピュータなどもターゲットになりそうだ。

その部品となるダイは、「Chiplet(チップレット)」と呼ばれることになる。Chipletを元にエコシステム(市場と言い換えてもいいだろう)を作ろうという構想だ。

既にIntel、AMDなどが異なるプロセスの複数のダイをワンパッケージに集積してプロセッサを作っている。この標準化は、いずれ表面化すべき動きではあった。

プレスリリースを見てみる(UCIeのプレスリリース「Leaders in semiconductors, packaging, IP suppliers, foundries, and cloud service providers join forces to standardize chiplet ecosystem[PDF]」)。設立の初期メンバーにはIntel、AMD、Google Cloud、Meta、Microsoft、Qualcomm、Samsungなどそうそうたる名前が並ぶ。

そして、製造側を代表する台湾の2大巨頭、TSMCとASE(パッケージ、組み立てなどの会社)が加わっている。メジャープレイヤーがそろっている。まさに「今後何十年か」使われる小さなシリコンチップの「大きな土俵」を作ろうという動きであるようにみえる。

「今後何十年」と書いたのは、「PCIe」を念頭に置いたからだ。そういえば、「UCIe」と「PCIe」はつづりもよく似ている。それを意識せずに「UCIe」という名前の規格にしたとは思われない。PCIeの先祖(?)でもあるPCIの発祥から数えると、PCIとPCIeはここ30年ほどのインターコネクト業界を牛耳っている規格の「一族」といっていいだろう。

PCIもPCIeも、もともとは拡張スロット間、あるいはPCB(プリント基板)上の半導体デバイス間の接続の規格であった。パッケージの「外側」のインターコネクト規格である。このPCIとPCIe規格があるおかげで多くの半導体メーカーの製品が相互に接続可能になっている。そしてPCI接続であるからこそ、ソフトウェアの底辺で働いているデバイスドライバなどの開発が統一的に行えてきた。

こういう標準規格の存在がなかったら、業界は混乱し、発展が阻害されたといっていいだろう。いまや一歩を踏み出す時期に来たというわけだ。新たな入れ物には、新たなエコシステムを作るための規格が何かほしいところなのだ。

コンピュータのインターコネクトの歴史を振り返る

昔を振り返ってみよう。PCIが登場したころのデバイス間のインターコネクト規格は乱立していた。当初のPC業界の標準はISA(Industry Standard Architecture)バスだったが、ISAバスでは、10年ほどでどうにもならない状況になってきた。

そして、EISA(Extended Industry Standard Architecture)、MCA(Micro Channel architecture)、VESA(VLバス)など複数の規格が並立してしまった。結構混沌として誰もが困った状況だったと記憶している。

しかし、PCIが登場した。真打登場という感じで急速に一本化され、またPCI自体も何世代かの改良を経て仕上がっていった。他のバスは駆逐された。その後、さらなる高速化のために物理層を高速シリアル新技術に変えようという機運が高まった折、PCIの覇権にも「分裂」の兆しがなかったわけではない。

そこで勝ち残ったインターコネクト技術はソフトウェア的にはPCI互換となり、PCIの名を冠するPCIeであった。そんなこんなで30年ほど、世界の縁の下の力持ちはPCIの名を冠する技術であるのだ。

UCIeにはPCIeとは異なる課題がある

異なるメーカー、異なるプロセスの複数のダイ(Chiplet)をワンパッケージにしようとする場合、パッケージに封止された半導体製品間のインターコネクト規格とは別次元の新たな問題が発生する。

パッケージの外側であれば、物理層の電気的特性、その上で動くプロトコルなどを決めてやる必要がある。さらにボード上の拡張コネクターなどに対しては物理的な形状なども規定する必要がある。しかし、そんな物理形状はパッケージに封入されているデバイスとは直接関係がない。

ところが、「Chiplet」といった場合、電気特性、プロトコルなど以外に、チップそのものの3次元的な物理形状やら、配線を取り出すためのバンプの位置、材質などから決める必要があるだろう。熱伝導も気になる。インターポーザ(貫通電極で表裏の回路を導通するための基板)の材質とかも特性に影響するだろう。

考慮しなければならないことは非常に多そうだ。また、ワンパッケージ内に集積することを考えると、テストのやり方とか、信頼性、リライアビリティ、故障解析など、対処が厄介な問題がいろいろありそうだ。実際にChipletで商売しようとすれば、実に広範囲な分野のもろもろの事項を取り決める必要が出てくるはずだ。そういう点で、PCIeなどのパッケージ外のインターコネクト規格を念頭に置いた規格のままでは、Chipletには不十分であるはず。新たな規格が必要とされる理由だ。

一方、電気的、プロトコル的な規格としては現行の「標準規格」であるPCIeをまずはそのまま「飲み込む」ようだ。これは必然ともいえる。パッケージの外でも中でもPCIeはそのまま使える。そして現状圧倒的に普及しているからだ。それにチップ外に出ていくことに比べれば圧倒的に配線の影響は小さくできるので、同じPCIeといっても消費電力などは格段に小さくできる。PCIeを外して規格は成立しないだろう。

UCIeとCXLとの関係

しかし、PCIe以外にも「CXL(Compute Express Link)」規格も取り込むようだ。CXL規格は主にサーバなどのハイエンドで使われ始めているCPUとデバイス間の高速インターコネクト技術だ。

UCIeのホワイトペーパーに「CXL」を見つけた時点で、新たに立ち上がったUCIeという標準化団体にちょっと疑念が生じた。UCIeのプレスリリース資料にある米国オレゴン州ビーバートン市という住所は、CXLの住所と一緒じゃないか。プレスリリース資料には表立ってメンバーとしてCXLは登場しない。UCIeが利用する接続技術の1つとしてCXLがちょこっと言及されているだけである。しかしUCIe、実はCXLと非常に近いか、メンバーが被っているのではないだろうか?

気になるのがCXLとの関係だ。CXLはサーバで使われる技術なので、メンバーにはHPE(Hewlett-Packardの法人向けビジネス部門で、大手スーパーコンピュータメーカーでもある)やDellなども入っている。まぁ、その辺の会社は、デバイス屋さんではないので、今回のUCIeに参加しないのは順当だろう。

しかし、CXLに入っていて、UCIeの初期メンバーに入っていない半導体会社が2社あることに気が付いた。1つはメモリのMicron Technologyであり、もう1つがNVIDIAである。どちらもChipletのエコシステムに入れば商売できそうな製品大手だ。加入するつもりだけれど何らかの社内外の手続き的な問題でまだ名を連ねていない(日本企業ならよくあることだが)のか、それとも袂を分かったのか。まだ迷っているのか? 気になるところである。

また、資料を読んでいるとUCIeの野望も垣間見えるのである。最初は「SerDes(コンピュータのバスなどで用いられるシリアル、パラレルを相互変換する回路)」で始める、というようなことが書いてある。「SerDes」つまりはPCIeなどで使われている高速シリアルの技術である。大変普及した技術であるので、どこの半導体会社も分かっているから、みんなにとってハードルが低い。

しかし「最初は」だ。今は「隠し玉」で特に言及されていないけれども、後からより高速高性能の技術の導入を考えているような書き振りなのである。パッケージ内ではPCIeにとって代わるようなものを考えているのかもしれない。

今後、数十年というのは当方の勝手な期待だが、多数の組織が参加するエコシステムを支えていく規格は、すぐに陳腐化するようでは困る。長年使える拡張性を持たせようとしているに違いない。多分、UCIeが世間に受け入れられた(つまりは参加者が増えた)と見たら矢継ぎ早に新版の規格が出てくると予想できる。その議論に加わり、情報を早く入手したければ早いところ加入しろよ、という感じか。

UCIeにある2つの懸念

必然的な規格と思いつつも、懸念がないわけでもない。第1はコストと利益配分だ。多数の会社のChipletを組み合わせるのはよいが、みんなが勝手に利益を載せたらとても高価なものになりかねない。

また、どこかの会社だけが暴利を貪って、他社にしわ寄せがいくようであれば、技術はよくても乗れない、という会社が出てくるだろう。いくらよい規格でも、コストが高いもの、あるいはもうからないものは普及しない。普及のためには時間とともにコストが下がるようなインセンティブが働くことも望ましい。

第2はアベイラビリティだ。これは昨今の半導体不足でみんなが身に染みている。多数のChipletを組み合わせるということは、何処か1カ所のサプライチェーンが切れると製造が全て止まるということだ。ユーザーも困るが、問題なくChipletを製造できている他のメーカーも困る。仕掛り在庫が積みあがってお金に変換されなくなるためだ。

この辺になると規格というよりビジネス、エコシステムの問題だが、技術だけでそういうところに目を背けていたのでは、こういう規格は成り立たないのではないかと思う。規格を超えたところで強靭なサプライ体制と共存共栄のビジネスモデルができなければ、うまくいかないだろう。

最後にもう一度書いておく。NVIDIAは入らないのか? 直近、そこが一番の関心事なのだが……。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

Copyright© Digital Advantage Corp. All Rights Reserved.