第278回 「AIがRISC-Vを設計」というニュースを読んで、はや失業(!?)かと思ったら……:頭脳放談

中国の研究チームが、人工知能(AI)ソフトウェアで「RISC-V」のCPUを自動設計したという。「何でもAI」という最近の風潮が、CPUの設計にまでと思い、論文を読んだところ、当初思っていたのとかなり違っていた。その違和感について勝手な意見を述べさせていただく。

人工知能が設計したというRISC-Vプロセッサ

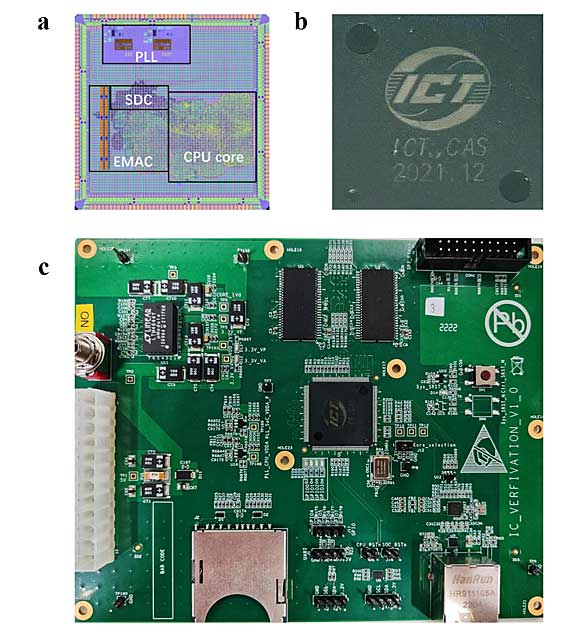

中国科学院/中国科学院大学を中心とした研究チームが開発した、人工知能(AI)で設計したRISC-Vプロセッサコア(写真:a)、そのパッケージ(写真:b)、評価用ボード(写真:c)。写真は、論文「Pushing the Limits of Machine Design: Automated CPU Design with AI[PDF]」より。

中国の研究チーム(中国科学院/中国科学院大学のShuyao Cheng氏などを中心としたチーム)が、人工知能(AI)ソフトウェアで「RISC-V」のCPUを自動設計したという論文が話題になっていた(論文は、「Pushing the Limits of Machine Design: Automated CPU Design with AI[PDF]」)。何でもかんでも「AI」といえばもてはやす風潮は収まっていない。

今度は、CPU設計もAIでか、ということで、ニュースバリューが上がったみたいだ。それに結果をIntelのCPUと比べているところも、一般の人に「分かりやすい」ようで、さまざまなニュースサイトが取り上げている。

論文を読んでいて、実はかなり違和感があったので、勝手な意見を述べさせていただく。結論からいえば、半導体におけるCAD技術の進歩の一環としては評価できるものの、世界(半導体業界)をひっくり返すほどの強烈なインパクトかというと疑問を感じた。

CPUはどうやって設計するの?

本題に入る前に、CPUをどうやって設計するのか、そのステップをざっくりおさらいしておく。

RISC-Vのような仕様が決まっているCPUの場合、通常は仕様書にそってマイクロアーキテクチャレベルから実装レベルまで順次設計に落としていくわけだが、現状その工程の多くで言語設計が採用されるのが普通だ。

言語設計も高いレベル(抽象度)から低いレベル(実ハードウェアに近い)までいろいろある。現行普及している比較的低レベル向き言語であるVerilogHDLやVHDLなどで記述できれば、ハードウェア要素部品への「コンパイル」は論理合成ソフトウェアが自動で行ってくれる。

端的にいえば、「これとあれを掛け算した後、それを足してね」といった手順を書けば、乗算器に加算器などが自動で作れてしまうわけだ。なお通常のコンピュータ言語とハードウェア記述言語の本質的違いは同時並列性にある。通常のコンピュータソフトウェアは基本的に順次処理であり、並列処理といってもスレッド程度だが、ハードウェアは基本全ロジックが同時並行に動作するからだ。

そして、論理合成後のネットリストというものは、物理設計に自動でマップできる。このレベルに達するのに何十年もかかったのだ。現段階のCAD技術をもってすれば、設計者にRISC-Vの仕様書を読んでVerilogで書き直せる力量があれば、取りあえず動作するCPUを作成するのは「たやすい」といえる。現在はFPGA技術が発展しているので大学生でもやろうと思えばハードウェア化できるし、やっている人もいると思う(根気があればだが)。

しかし、だ。商売になるような設計にするとなると、格段に難易度が高くなる。単に仕様書に書いてある通りに命令が動くということでなく、性能(1命令当たりのクロック数と動作周波数、そして消費電力)とコスト(チップ面積)で同業他社のレベルを凌駕(りょうが)しないとならないからだ。この部分が設計ベンダー各社のお金を取れるポイントなのである。

また、こういう実装に近い部分には特許が大量に出願されている。むやみな設計を行うと、誰かの特許を踏んでしまい、最悪出荷差し止めとなる。特許は知らなかったでは済まないので、他社の実装方式の調査は「無」にはできない。

さらにいえば、RISC-Vのようなケースでは、RISC-Vインターナショナルが仕様を決めてくれている上に、その仕様は実装しやすいような配慮までされている。そして、シンプルである。やりやすいのだ。

しかし、仕様が決まっていない本当にまっさらな状態からCPUを設計しようとすると、考慮しなければならないトレードオフはあまりに多い。その割にそれが売れるかという観点からいうと、リスクが高い。無名のアーキテクチャを売れるようにするためにかかる主としてマーケティング的なリソースは膨大だ(RISC-Vの場合は、RISC-Vインターナショナルがそのマーケティングを担ってくれている)。

AIによるCPUの設計手法

さて本題の今回の発表を見ていこう。一番注目されるのは、その設計手法である。上に述べたような言語設計手法は採用していない。現代、AIによるソフトウェアの自動コーディングは普通に行われるようになっているのでハードウェア記述言語に対してもできると思うが、そういう手法はとっていない。

採用したのは、膨大な入力と出力ベクトルの組み合わせをAIに学習させて、論理を自動生成するという手法だ。その際、Binary Speculation Diagram(BSD)というグラフを使っているようだ。

ここを読むと論理回路の設計者的には、「何だ、入出力の組み合わせからCPU相当のFSM(Finite State Machine、有限状態機械)を一気に自動生成しているだけではないか」という感想が出る。

ある入力信号の組を論理回路に入力すると、いつも同じ出力が得られるのであれば組み合わせ回路だ。一方、入力信号が同じでも論理回路の内部の状態(端的にいえばフリップ・フロップの記憶)によって出力が異なってくるのが順序回路、すなわちFSMである。

CPUというものも順序回路の1種なのである(ただし記憶している履歴の量が半端ない)。こういう回路の自動生成技術は古くから研究されており40年以上前から一部は実用化されていた。

ただし、組み合わせ爆発が起こりやすく、最適解を求めるのが困難な分野であったので、そのときの計算機の性能とメモリ量と相談して、実用になる範囲で使われてきた、ということだ。

つまり、1個の大きな問題を丸ごと解こうとすると計算時間が爆発するので、小分けにして小部分(モジュール)ごとに適用した後、組み立てるといった技を使うわけである。また、論理の最適化を行う場合にグラフ理論を使うのも割と普通じゃないかと思う。

そういう観点からいうと、「どこまで独創的なの?」とも思えてしまう。まぁ、CPUを丸ごと1個、自動生成するような荒業を普通はしないと思うのでこれはこれで一歩前進か。

ただ、ターゲットにしているRISC-Vの整数型32ビットのコアは、非常に素直でやりやすいターゲットでないだろうか。ハードウェアに実装しなければならない命令の数は少なく、そしてシステマチックである。やりやすいところでまずは実装して実績を積んでみた、というところか。

また、Linuxがブートするところまで実際に動かしたという点では単なる論文ベースでなくて説得力が大きい。

何でIntel486SXと比較する?

しかしだ、Intel486SXの設計にかかった工数や性能と比べているのはどうかと思う。「486」の名前を出せば一般受けするからという、ウケ狙いな意図がありありと感じられる比較対象だ。

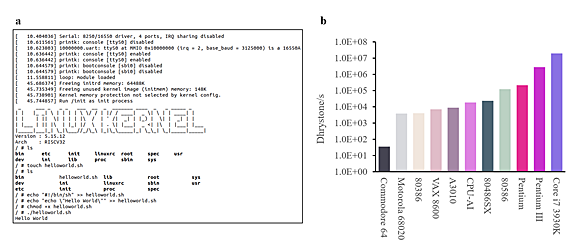

AIで設計したRISC-Vプロセッサで実行したLinuxと性能

AIで設計したRISC-Vプロセッサで実行したLinuxの画面(画面:a)と、各種プロセッサとの性能比較(グラフ:b)。Intel486SXに少し届かないレベルを実現したとしている。図は、論文「Pushing the Limits of Machine Design: Automated CPU Design with AI[PDF]」より。

Intel486SXが設計されていた時代(1980年代後半)は、言語設計も論理合成も存在こそすれ、まだそれほど進歩していなかった。Intelはそれなりに先進的だったので、既に自社開発の合成ツールや自動レイアウトツールなど駆使していたはずだが、チップ全体を一撃で合成できるような代物ではなかった。当時自動化できたのはごくごく小さなブロックだったはずである。

だいたいCPUを設計するのに使っていたコンピュータも今とは段違いで非力である。486の一世代前になるが、386のアーキテクトだったJohn H. Crawford(ジョン・H・クロウフォード)氏は、自分の机のところにmicroVAX(DECのミニコンピュータ)を持っていて占有していた。

「スターアーキテクトは違うなぁ」とうらやましく思ったが、microVAXの性能は1MIPSを割り込んでいた程度だったと思う。そんな環境下で、膨大な人数と時間をかけて設計したという数字と、現代のマシン上でAIを使ったら5時間で自動生成できたという数字を比べるのに意味があるのかと言いたい。

それにx86系は、屋上屋を架すような作りで、歴史と伝統に基づいた例外に次ぐ例外、数百クロックなど当たり前の深い深いステートマシンが特徴のCISCである。

それと、シンプルでエレガントなRISC-Vを比べること自体、論外な気がする。どちらかといえば、VerilogかVHDLで言語設計された同レベルの仕様のRISC-Vで、そのコーディング時間とコンパイル時間、そしてできたネットリストの回路規模と性能を総合的に比較するのが、「正々堂々」っていうものではないだろうか。

この手法には根源的な問題が……

さらにいえば、この技術を一気にCPUレベルに適用するのには根源的な問題があると思う。つまり設計ターゲットの入出力ベクターが事前に確定(もっといえば、コンピュータとしてバグなく動作すると言い切れるレベルで)していないとならないという点だ。

既存のCPUの動作モデルや実機があれば、入出力ベクターを用意することはできる。ただし、そのベクターが「十分」なのかどうかは、モデルや実機で別途検証されていなければならない。

この手法では、出発点となるモデルと同等の回路を生成することはできるが、上回る性能とする手法は明確ではない。結局、より性能の高いCPUを設計するには、上流工程の動作モデルを別に作って検証する必要がある、ということであれば、CPU設計全体を自動化したとはいえないように思われる。既存の設計フローにおけるバックエンドの一部を置き換えるにすぎない、ということにならないだろうか。

この設計技術が、部品としてのFSMの設計技術として効果が高い、ということであれば、昔のIntel486SXなどと比べるのではなく、現在のCADソフトウェアとの比較でその性能を語ってもらいたい。あるいはCPU設計技術として段違いの技術だということであれば、実際に最先端のRISC-V機の設計に適用してみせるべきだろう。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

Copyright© Digital Advantage Corp. All Rights Reserved.