第293回 Cerebrasが仕掛ける「1ウエハー=1チップ」のAIアクセラレーターはNVIDIAを超えるのか?:頭脳放談

人工知能(AI)分野がノーベル賞を受賞するなど、相変わらずAIへの注目は高い。そんな中、「Cerebras Systems」という会社が、「Wafer-scale Integration」という1990年代に研究が盛んだった技術を使ってAIアクセラレーターを開発しているという。このWafer-scale integrationという技術の歴史と問題点、Cerebrasに勝ち目があるのかどうかを筆者が解説する。

Cerebrasが仕掛ける「1ウエハー=1チップ」のAIアクセラレーター

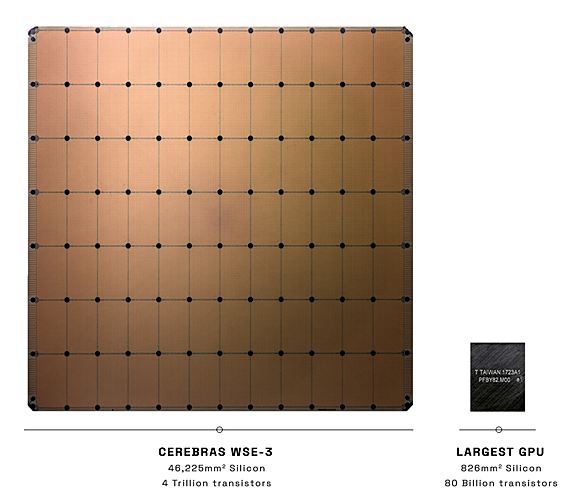

Cerebras Systemsが開発したディープラーニング専用のプロセッサ「ウェハースケールエンジン(WSE-3)」とGPUとの比較。1ウエハー=1チップのWafer-scale integrationを採用するため、巨大なプロセッササイズとなっている。Wafer-scale integrationという技術の歴史と問題点、Cerebrasに勝ち目があるのかを筆者が解説する。写真は、Cerebras SystemsのWebページ「The Wafer-Scale Advantage」より。

人工知能(AI)分野へのノーベル賞の話もあり、AIは依然盛り上がっている。そんなAI分野の中で過去の亡霊のような言葉を最近再び聞くようになった。「Wafer-scale integration」という言葉である。古くから研究され、1990年代には結構いいところまで出来上がった技術である。1枚の半導体ウエハー上にシステムの中核部分全てを載せてしまおうという意欲的な技術だ。今回は、この技術に着目してみたい。

Wafer-scale integrationの技術的な問題点

チップ(ダイ)とウエハーのサイズを考えれば、数百倍もの面積の差がある。その大面積の上にチップにしたら数十個から数百個になる回路を1つにまとめてしまおうという。チップをパッケージに詰めてプリント基板上に配置する従来型のシステムに比べれば、はるかに高速で高密度な接続が可能だ。当時、高性能なコンピュータを作るための技術として盛んに研究されていた。

しかし、1990年代、あと一歩、既存技術を超えるコストパフォーマンスの壁を越えられずにブレークできずに終わったと記憶している。当時ブレークはできなかったが、技術そのものは死なず、市場的には辺境でほそぼそと開発が続いていたようだ。

Wafer-scale integrationの何が難しいのか

Wafer-scale integrationの何が難しかったかを簡単に振り返りたい。半導体製造には欠陥(ディフェクト)が発生することは避けられない。単純化した話をする。プロセス的には1枚のウエハー当たり10カ所の欠陥が避けられないとしよう。また1枚のウエハー当たり100個のチップが載せられるとしよう。すると1枚のウエハーのうち10個以下(たまたま複数個の欠陥が1つのチップに載ることもあるので「以下」だ)が不良となり、残りは良品となる。つまり90個より多いチップが良品になるということだ。これなら商売が成り立つ(後は製造する製品のスペック次第だが)。

ここで同じ条件下のプロセスで、1枚のウエハーをそのまま製品にしようとする。何もしなければ1枚のウエハーに10カ所の欠陥があるのだ。ほぼ必ず欠陥品になってしまうことになる。商売にならんということだ。

当然、欠陥を少なくする努力は必要だがゼロにはできない。そこでウエハースケールでの集積の場合、回路に冗長性を持たせ、欠陥が発生しても代替回路で置き換えるような仕組みを形成することで、欠陥があるウエハーからでも完全にスペックを満たす(当然欠陥がないときよりは、容量その他は低下することになる)製品を作り出す、といった技術開発が必要だったのだ。もちろんそれに関してテスト技術その他、特有の関連技術多数が必要になった。

1990年代のWafer-scale integrationはどうなった?

当時のシリコンバレーに「Waferscale Integration Inc.(WSI)」という名のそのものズバリの会社名を掲げた会社があった。WSIについて誰だったか忘れたが書いていたものを読んだ記憶がある。「99%の問題は解決したが、100%にはできなかった」という。後一歩に迫ったくやしさがこもっている感じだ。

WSI自体は開発した技術を流用したらしい不揮発メモリとプログラマブルロジックの会社に変化した後(本業が売れなかった後の苦し紛れの脱出経路かもしれない)、STMicroelectronicsに買収されている。既に四半世紀も前の2000年9月の話である。

ただし、回路の冗長化などにより欠陥があっても一定の収量を確保する技術は、その後一般化している。チップサイズが大きくなり、巨大なキャッシュメモリなどを搭載する品種が増えて、欠陥の影響を局在化する技術を導入しないともうかる商売にならなくなったためだ。そういう点でWafer-scale integrationは当時ビジネス的には失敗であったが、後につながる技術だったといえる。

Cerebras Systemsが再びWafer-scale integration技術をよみがえらせる?

さて、そんな技術が今なぜまた注目(AI分野と見れば物色している投資家の皆さんにだが)されているのか? それは、「Cerebras Systems(以下、Cerebras)」という会社が近い将来株式公開(IPO)をしそうだという期待からである。日本では東京エレクトロンデバイス(TED)が代理店をしている。

Cerebrasという会社が何を作っているのか? Wafer-scale integration技術を使い300mmウエハーから採れる最大サイズの巨大なチップ上に構成したディープラーニングシステムを作っているのだ。現行製品のWSE-2で21.5cm(215mm角)という巨大さである。

積和演算のコア数で85万個という。NVIDIAのデータセンター向けGPUで1個当たり5000から1万個程度のコア数である。NVIDIAのボード何十枚分かの演算能力を1枚のボードで置き換えられるのだから、段違いの集積度だ。これをデータセンター向けの通常のラックにスッポリと収まるサイズに製品化しているようだ。巨大化するデータセンターにしたら装置の大きさだけ見ても魅力かもしれない。

そしてチップ内での信号接続は一度チップ外に出るよりも速く、そして本数も稼げる。速度的にも消費電力的にもアドバンテージがあるはずだ。なお、そのチップの巨大さからしてもNVIDIAのようなデスクトップ向けはありえず、データセンター一択のビジネスである。

CerebrasのWSE-2を搭載するディープラーニングシステム

Cerebrasのウェハースケールエンジン「WSE-2」を搭載するディープラーニングシステム「CS-2」。19インチラックに搭載可能な15Uのディープラーニング専用システムとなっている。写真は、東京エレクトロンデバイスのWebページ「Cerebras | CS-2」より。

つまり、この会社の「IPOするかも」という情報に注目している投資家の皆さんが期待する先に、時価総額ウン百兆円に達するNIVIDAをヒックリ返すのではないかという思惑があるのだと思う。IPOが先なのか、新機種「WSE-3」が先なのかは分からないが、Cerebrasも当然そうなる未来図を描いているのだろう。

Cerebrasが巨大なデータセンタビジネスをさらっていく可能性も

AIというとハードウェアを活用するためのソフトウェアも必要だ。NVIDIAの巨大な株価はかなりの部分、多くのAIソフトウェアがNVIDIAのハードウェアを当てにしている、という点にかかっていると思う。

ただし、AI分野はプラットフォーム化も進展していて、メジャーな売れ筋のソフトウェアプラットフォームをサポートしていけば、市場参入の障壁は大分下げられるようだ。Cerebrasとしては投資家から集めた巨額資金でソフトウェアにも相当投資しているのだろう。実際に使ってみたことはないので何とも言えないが、使えるレベルにあるみたいだ。

AI分野の動きは速い。ひとたび、Cerebrasがハードウェアのトップに躍り出て、それに乗っかる人々が大挙して押し寄せたら巨大なデータセンタビジネスを一気にさらっていく可能性もあるだろう。

というわけで、目の色が変わってしまった人もおられるかもしれない。一方的にならないように懸念点も書いておく。

Cerebrasの懸念材料

その主たるところは、チップサイズを増大する(Cerebrasは究極の1ウエハー=1チップである)という方向性は、現時点での時代の潮流からすると逆行する方向であることだ。現在多くの開発が「チップレット」と呼ばれる、小さめのチップを複数組み合わせてシステムを組み上げる方向に向かっている。その方がチップサイズの増大に伴う高度な冗長性など必要とせずイールド(歩留まり)も上げられるからだ。

また、異なるプロセス技術を活用し、ロジックとメモリをそれぞれ最適なプロセスで製造するなどのアドバンテージもある。当然、チップ間の接続はウエハースケールよりは不利になるが、最近ではチップレットをサポートするための高速で高集積なパッケージング技術が開発されている。日々、速度も集積度も向上中といえる。つまり、現行の主流派の方向性(それはNVIDIAの方向性でもある)でも問題解決ができないわけでない、ということだ。

従って、現行の主流派と真正面からぶつかってコストパフォーマンスで凌駕(りょうが)できないと大成功はない。さもなければ「Wafer-scale integrationは、後ちょっとだったんだけどね」などと言って再びニッチなところに押し込められて雌伏を余儀なくされるかもしれない。

ソフトウェアとハードウェアの立場は異なるが、今やAIの主流であるニューラルネットワーク(NN)技術も20世紀にブレークしかかったときはダメだった。しかし、その後も研究は続き、年寄からするとごく最近になって地下の奥底からよみがえって世界を制覇することになった感じだ。Wafer-scale integration技術がそうならないとは言えないし、なるとも言えないのだが。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

Copyright© Digital Advantage Corp. All Rights Reserved.