|

連載 IT管理者のためのPCエンサイクロペディア 第9回 PCのエンジン「プロセッサ」の歴史(3)〜商業的には失敗だった「Pentium Pro」の功績 元麻布春男 |

|

大成功を収めたP6アーキテクチャの特徴

その立役者であるP6マイクロアーキテクチャだが、x86といいながら事実上はRISCプロセッサであることはすでに述べたとおり。だが、単なるRISCプロセッサではなく、当時最先端のRISCプロセッサとほぼ同等の機能を備えていた。すなわち、最大3命令をディスパッチ可能なスーパースケーラ・アーキテクチャ、12段と当時としては非常に深いスーパー・パイプラインをはじめ、Intelがダイナミック・エクゼキューション・アーキテクチャと呼ぶアウト・オブ・オーダー実行、動的分岐予測、投機実行、データ・フロー解析といった当時の最新の機能を備えている。

こうしたエンジンを支えるため、P6マイクロアーキテクチャでは2次キャッシュ・バスを、プロセッサのシステム・バスから分離することで広い帯域を確保した。そしてプロセッサの外部には出てこない2次キャッシュ・バスをバック・サイド・バス(BSB)、チップセットに接続するシステム・バスをフロント・サイド・バス(FSB)と呼んだ。現在も使われる「FSB」という用語は、P6マイクロアーキテクチャと同時に生まれたものだ。当時P6マイクロアーキテクチャがBSBとFSBの2つを持ち、広い帯域をサポート可能であることに対し、キャッシュ・バスとシステム・バスが分離されていないSocket 7アーキテクチャのプロセッサ(自社のPentiumプロセッサだけでなく、AMDやCyrixの互換プロセッサを含む)をIntelは「死の谷」とやゆしたものである。蛇足になるが、IntelはP6マイクロアーキテクチャでありながら、2次キャッシュをサポートしないCovington(コビントン)コアのCeleronを出さざるを得なくなり、「死の谷」はどこにいった? と逆にやゆされることとなる。

P6マイクロアーキテクチャのシステム・バスは、バスに対するデータの要求と受け取りがスプリット(分離)された、いわゆるスプリット・トランザクションをサポートしている。実際には、必ずバス・トランザクションがスプリットされるわけではなく、時間がかかる場合のみ、いったんバスを解放し、ほかのトランザクションを開始する(例外的にスプリットされる)仕様となっており、純粋なスプリット・トランザクションとは若干異なる。P6マイクロアーキテクチャのシステム・バスでは、完了していないトランザクションの数は、バス・プロトコルとしては最大8つ、プロセッサ単位では最大4つとなっているが、これはシステム・バスが複数のプロセッサ(最大4つ)で共有されることが想定されているからである。

|

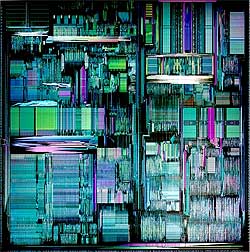

| Pentium Proのプロセッサ・ダイ |

| Pentiumに比べて複雑な構造になっていることがダイの写真からもうかがえる。右下がバス・インターフェイス・ユニットで意外と大きな面積を占めている。また、左中央部分がuopsに分解された命令を実行ユニットにわたすためのリザベーション・ステーションになる。 |

スプリット・トランザクションをサポートすることの利点は、時間のかかるトランザクションにバスを占有されないため、バスの使用効率が高くなることだ。しかし、マルチプロセッサ構成を前提にデザインされたP6のシステム・バスの帯域は、逆に1つのプロセッサでは使い切れないことにもなる。実際、1個のPentium Proによるシステム・バスの占有率は20%程度といわれる。P6マイクロアーキテクチャのFSBクロックが、66MHz、100MHz、133MHzと引き上げられ、対応メモリがFPM(Fast Page Mode)、EDO(Extended Data Out)、PC66 SDRAM、PC100 SDRAM、PC133 SDRAM、PC800 RDRAMと高速化していったにもかかわらず、それが性能に大きく反映されなかったのは、プロセッサが高速な2次キャッシュを内蔵していることに加え、こうしたバスの特性もあってのことだと考えられる。結果的に、外部の低速なメモリなどの悪影響を受けにくい半面、メモリやFSBが高速化することによる恩恵も受けにくい、というわけだ。

FSBは、チップセットやソケット・レベルでの互換性を維持するため、動作クロックの引き上げ以外に大きな変更が難しい。それに対し、外部に影響しない2次キャッシュ用のBSBは、P6マイクロアーキテクチャを採用したプロセッサの変遷にともない、何度か大きな変更が加えられることになる。なお、最初に登場してきたPentium Proでは、2次キャッシュ・バスはプロセッサ・コアと同じ動作クロックで駆動される64bit幅のものである。ここに256Kbytes、512Kbytes、1Mbytesのいずれかのサイズの2次キャッシュが接続された。

36bitに拡張されたアドレス・バス

さて、P6マイクロアーキテクチャのもう1つの特徴は、アドレス・バスを36bitに拡張したことにある。すなわち、アドレス・バスが32bitで4Gbytesの物理メモリ空間をサポート可能なPentiumに対し、P6マイクロアーキテクチャのプロセッサでは、最大で64Gbytesの物理メモリをサポートすることができる。もちろん実際には、P6マイクロアーキテクチャのプロセッサに用意された一般PC向けのチップセットで、このような大容量メモリをサポートしたものは存在しないし、内蔵する2次キャッシュは4Gbytesまでのアドレスしかサポートできない(Pentium IIの初期モデルは512Mbytesまで)。ただ、現在使われているWindows NT/2000/XPのクライアントOSにおける、最大メモリ4Gbytes、1プロセス当たり2Gbytesという制約は、32bit CPUであるP6コアのプロセッサの仕様によるものではない(ハードウェア的にはすでに解決済みである)、ということだ。

もう1つ、Pentium Proで異例だったのは、リリースに際してUser Test Program(UTP)という一種のパブリック・ベータが実施されたことだ。Pentium Proを実際にリリースする前に、さまざまなユーザー・アプリケーションで動作を確認しようというもので、初期にはリリースされなかったPentium Pro-133MHzが提供された。このような慎重姿勢は、Pentium Proがサーバ/ワークステーション用だったというだけでなく、Pentiumプロセッサに浮動小数点演算のバグが見付かったことも影響しているハズだ(コラム参照)。なお、UTPに申し込んだもののテスターに選ばれなかったユーザーには、おわびの手紙とともにPentium Proのダイ写真を用いたポスターが送付された(筆者はいまも捨てずに手元に残してある)。

|

Pentiumの浮動小数点演算のバグとその解決 Intelは、これをPentiumのバグと認め、バグを修正したものとの交換を実施した。当時、PentiumにはBoxedと呼ばれるリテール製品はなく、基本的にはすべてOEM製品ばかりだったのだが、IntelはPCベンダ(OEMベンダ)経由の交換だけでなく、自社による直接交換も行った。これは、A社のテレビに使われているB社のCRT(ブラウン管)を、B社が直接交換するようなもので、極めて異例のことであった。しかし、Intel自身が交換を行わなければ、交換不可能なユーザーが必ず生じてしまっただろう(いわゆる「自作」やホワイトボックス系のPCを使うユーザーなど)。Intelが期限を設けず、対象を限定せず、広く交換に応じたことから、この問題は速やかに沈静化した。 この危機に際し、Intel社内で問題の処理に当たったのが、当時のアンディ・グローブ(Andy Grove)CEOのテクニカル・アシスタントであったショーン・マローニ(Sean Maloney)氏だ。この問題をうまく切り抜けたことをきっかけに、マローニ氏は出世コースに乗った感がある。問題が解決した1995年、マローニ氏はアジア太平洋地区の責任者に任命され、その後セールス・マーケティング・グループのトップを務めた。現在は取締役副社長として、通信機器事業部(ICG)のトップの座にある。 |

次回は、Pentium Proの後継となるPentium IIならびにCeleronについて解説していこう。![]()

| INDEX | ||

| 第9回 PCのエンジン「プロセッサ」の歴史(3)〜商業的には失敗だった「Pentium Pro」の功績 | ||

| 1.P6マイクロアーキテクチャの誕生 | ||

| 2.RISCアーキテクチャを極めたP6マイクロアーキテクチャ | ||

| 「System Insiderの連載」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|