ザイリンクス、OpenCL、C/C++でFPGAアクセラレーションを行う開発環境最新版のリリースを発表:電力消費効率をCPU/GPUの25倍に高める

ザイリンクスは5月26日(米国時間)、FPGAを使用したアクセラレーター開発環境の最新版「SDAccel開発環境2015.1」のリリースを発表した。最新版では、統合開発環境の機能が強化され、対応ライブラリも拡充される。

FPGA大手ベンダーのザイリンクスは5月26日(米国時間)、FPGAを使用したハードウエアアクセラレーター開発環境「SDAccel開発環境」(以下、SDAccel)最新版のリリースを発表した。最新版となる「2015.1」では、Eclipseベースの統合開発環境である「SDAccel IDE」の機能が強化された。また、新たに提携企業を加えることにより、対応ライブラリを拡充した。

ソフトウエア開発者にもなじみやすいFPGA開発環境を実現

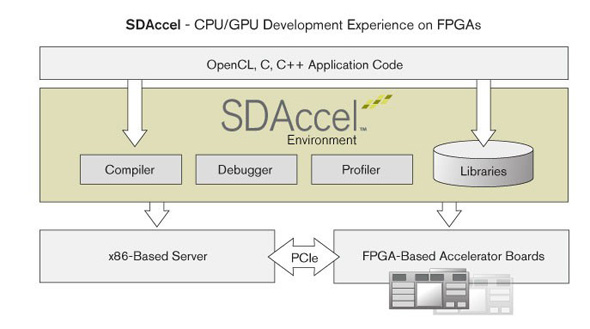

SDAccelは、既存のサーバーなどの処理性能を高めるために、CPUを補助するアクセラレーターとして、PCIeバスなどに接続されるハードウエアおよびソフトウエアだ。

従来のFPGA(Field-Programmable Gate Array)を使用したアクセラレーター開発では、ハードウエア記述言語(HDL)と呼ばれるハードウエア開発特有の言語を使用しなければならず、ハードウエア開発になじみのないエンジニアにとっては、C言語などの高級言語が使用できるCPU/GPU(Graphics Processing Unit)に比べて、開発難易度が高かった。

SDAccelは、従来CPU/GPU開発で使用されてきたOpenCL、C/C++に対応しており、ハードウエア開発の経験がないソフトウエアエンジニアでも、容易にFPGAアクセラレーションを行うことができる。

CPU/GPUを超える電力性能

近年では、電力性能の良さや大手企業がデータセンターに採用したことなどからFPGAに注目が集まっており(参考記事「頭脳放談:第181回 Intelが167億ドルで手に入れるもの 」)、ザイリンクスは開発環境を整備することで、データセンターでのFPGAアクセラレーションを推進する狙いだ。

ザイリンクスの調査によれば、SDAccelで開発されたFPGAソリューションは、他の開発環境で生成されたソリューションと比較し、3倍のスループットを発揮するという。また、CPU/GPUと比べて、データセンターアプリケーションのワットパフォーマンスを最大25倍に向上させるという研究結果も得られている。

Copyright © ITmedia, Inc. All Rights Reserved.