第241回 CoreとAtomを重ねて実装、新プロセッサ「Lakefield」の技術的挑戦:頭脳放談

Intelから新しい第10世代のCoreプロセッサが発売された。開発コード名「Lakefield」と呼ばれるモバイル向けのプロセッサだ。Microsoftからは、デュアルスクリーンデバイスの「Surface Neo」に採用することが発表されている。このLakefieldとはどのようなプロセッサなのかを明らかにする。

2019年あたりから断片的に公表されていたIntelの新技術群が1つの現物製品としてリリースされた(Intelのプレスリリース「Intel Hybrid Processors: Uncompromised PC Experiences for Innovative Form Factors Like Foldables, Dual Screens」)。「Lakefield(レイクフィールド)」なる開発コード名を与えられたCoreプロセッサ2種である。

| プロセッサナンバー | i5-L16G7 | i3-L13G4 |

|---|---|---|

| グラフィックス | Intel UHD Graphics | Intel UHD Graphics |

| コア/スレッド | 5/5 | 5/5 |

| グラフィックス(実行ユニット数)[個] | 64 | 48 |

| キャッシュ容量[MB] | 4 | 4 |

| TDP[W] | 7 | 7 |

| ベース動作周波数[GHz] | 1.4 | 0.8 |

| ターボブースト時の最大周波数(シングルコア)[GHz] | 3.0 | 2.8 |

| ターボブースト時の最大周波数(全コア)[GHz] | 1.8 | 1.3 |

| グラフィックス最大動作周波数[GHz] | 0.5 | 0.5 |

| 搭載メモリチップ | LPDDR4X-4267 | LPDDR4X-4267 |

| 販売開始となったLakefieldの主な仕様 | ||

一応、「Core i5」と「Core i3」に分類された型番が付与されてはいるものの、その差は一部機能のユニット数や動作クロックの上限などだけに見える。よくやる手だろうが、同じダイ(以降チップと呼ぶ)を共用して、2製品を作り分けているだけのようだ。実質的には1つの製品だろう。

Lakefieldの用途は、モバイルだ。最初に市場に現れる応用製品が折りたためる画面を持ったノートPCであったり、2画面のタブレットであったり、と一般ユーザーに対してマーケティング的な目新しさをアピールするにはもってこいだ。

Lakefieldを搭載する主なノートPC形状

Lakefieldを搭載する主なノートPC形状Lakefieldは、超薄型のノートPCや2画面のタブレットなどに搭載される予定だ。こうした新しいフォームファクタを実現するために周辺ロジックまで含めた高密度な実装を実現している。「New Intel Core Processors with Intel Hybrid Technology」より。

Lakefieldの技術的なポイント

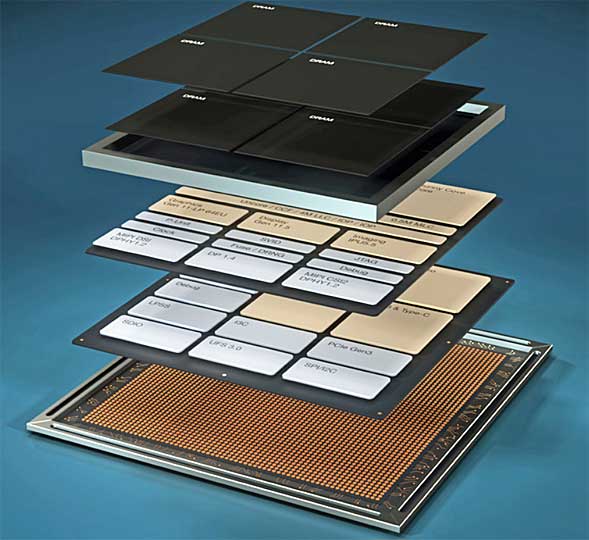

だが、「いつもの」Intelの新製品のアップデートと一線を画するLakefieldの技術ポイントは幾つかある。その最大なものが3次元実装を使った非常に集積度の高いパッケージングである。12mm角、1mm厚という体積の中に、各種の周辺機能を集積したロジックチップ、CPUやGPUなど処理の中心となる機能を集めたチップ、そしてDRAM2層と、4個のチップを重ねている。x86史上最高と思われる集積度だろう。

Lakefieldの実装

Lakefieldの実装図のようにメインのプロセッサ上にロジックやDRAMなどを3次元で実装している。「New Intel Core Processors with Intel Hybrid Technology」より。

従来も平面的にチップを並べる2次元的なマルチチップパッケージや、ロジックチップ1層の上にメモリを積むような集積はままあった。メモリなどは重なっているのが当たり前の世の中になったし、スマートフォンなどは重ねられたチップで一杯といえる。

しかし、筆者のように頭の古いものからするとx86のような消費電力が大きなCPUをハンバーガーのビーフパティよろしく上下のチップで挟み込むような実装が、本当にできるとは思っていなかった。x86の発熱デカイというのが思い込みだったのだ。当然、真ん中が発熱し過ぎたらシステムとして成り立たない。この製品におけるx86の消費電力は低い。

特に待機時電力は超低い。Intelの出した数字は従来の10分の1だ。言い過ぎかもしれないが、Armと遜色なくなっている。この製品一世代で達成したわけではないが、技術の積み重ねによってArmにできることはx86にもできるようになっていた、ということのようだ。

ロジックチップ2層の積み重ねには、「TSV技術(貫通ビア)」を活用している。半導体のチップというのは、ウエハの表面にのみ回路を形成する。これを重ねる場合、片方を裏返して表面同士を貼り付けて(間の接続材料はいるが)2層という方法がある。

しかし、これだと2枚でおしまいなので、3枚以上は同じ方向を向けて張り合わせ、チップの側面方向に縦方向の配線を伸ばして側面から接続していく方法がとられることが多い。

多機能なロジックチップの場合、配線本数が非常に多いので側面では足りない。そのため、チップに穴を開けて縦方向に信号を通してしまう。これを「TSV(Through-Silicon Via)」と呼ぶ。多分、放熱にも効くのではないかと想像する。こういう高集積なモジュールだとモジュール内の熱設計のシミュレーションなど相当に複雑そうである。TSVは各社取り組んでいて、Intelだけの技術ではないが、「攻めた」実装技術であることは確かだ。

これを全面的に使い、下のロジックチップと中のCPU/GPUチップを結合している。このおかげで、下のベースチップは製造技術22nm、中のCPU/GPUチップは10nmと異なるプロセスのハイブリッドが可能となった。頭脳放談「第230回 AMD Ryzenが高コストパフォーマンスを実現した3つの理由」でも書いたが、全部のIP(半導体のデザイン)を最先端の同一プロセスでそろえるのは時間もかかるし、特性的にも無理があることが多い。このような別チップをスタックする形で異プロセスを組み合わせるのが現時点では最適解ではないかと思える。

そして最上層にはDRAM2枚を重ねたDRAMパッケージをパッケージオンパッケージで搭載しているようだ。おとしめているわけではない、真に「屋上屋を重ねる(本来は、「屋下に屋を架す」が正しいが、この場合は誤用の「屋上屋を重ねる」の方が意味合い的には近いだろう)やり方である。

パッケージも小さいが、それを搭載する基板のフォームファクタも大幅向上している。Intelのプレス資料をそのまま受け取るならば基板面積で47%減である。ただ、比較対象の基板は、第8世代のCore i7のものだ。第10世代のCore i5に位置付けられるLakefieldと比べている点、マーケティング的に「半減以下」という数字を印象付けたくて、多少盛っている感はなくはない。

しかし、基板上にはコネクター類とか物理的に小さくできないものがかなりある。CPU周辺が小さくなっても、小さくできない部分があるのにもかかわらず、ずいぶんと縮小できているのは間違いない。12mm角にほぼ全ての中核部品が収まってしまっている効果は大きい。

こういう製品を出してきたIntelの意図は、対Armじゃないかと想像するのは当然だろう。Armがサーバ機にまで攻め込んできている中、反対にArmの牙城のモバイルに攻め込む、あるいは、Armの上でWindows 10が走ってしまう昨今、今まで保持してきたPC世界をArmに奪われまい、という防衛。しかし、現行ビジネス的には、実際は対AMDという想定も正しいのではないかと思う。過去、Intel一色だったブランドメーカー製のノートPCでAMDのZen2シリーズ(Ryzen)の採用がしきりだ。そういう奴らの鼻先に一発打ち込んでやったという感じもなくはない。

小さいコアと大きなコアを組み合わせたLakefield

Arm対抗という観点で言えば、CPUのコア構成も今までのx86になかったユニークなものとなっている。5コア構成なのだ。小さい「Tremont(トレモント)」コアが4コア、大きい「Sunny Cove(サニー・コーブ)」コアが1コアである。小さい方のTremontコアはAtom系のコアにフロントエンドの改良を施したもののようだ。大きい方のSunny Coveが従来のCoreマイクロアーキテクチャ直系である。

小さいコアと大きいコアの組み合わせというとArmの「big.LITTLE」がすぐに思い出されるが、それとは少し違うと思う。もともとbig.LITTLEは、ソフトウェアが互換の小さいコア群と大きいコア群の2セットを持たせ、負荷が軽くて電力消費を抑えたいときは小さいコア群、負荷が重くなって性能を出さねばならないときは大きいコア群と切り替えて使うという発想であった。

ソフトウェアからみたら4コア4スレッドの環境でずっと動いているのだが、いつの間にかスレッドを動作させているCPUが大きいやつに(あるいは小さいやつに)切り替わっている、という感じだ。ソフトウェアでこのコアを御指名とかいう制御はなくて済む発想だ。

big.LITTLEは、ディフェンス(低消費電力)チームとオフェンス(高性能)チームを総入れ替えするアメリカンフットボールのようなシステムと言えよう。これに対してLakefieldは、ソフトウェア的にはホモに見えるけれども、性能的にはヘテロなコアを使い分ける感じ、というと説明になっていないか。

この仕事は大きい方のコアでお願いとか、この仕事は小さい方でOKとか仕事ごとに割り振りしないとならないはずなのだ。シングルスレッド性能が高いはずのSunny Coveと(当然ゲームなどはこちらに割り当てたいだろう)、細かい仕事多数をやり続けさせる(通信とかOSとかシステム全般のあれこれ)のに適するはずのTremontに、それぞれ最適な仕事を割り振らないとならない。

当然、OSがこの割り振りをしっかりやってくれないと思ったような性能は出ない。しかし、心配はなさそうだ、今回、Microsoftのモバイル製品「Surface Neo」もLakefieldを採用する(「Microsoft、初のLakefield搭載デバイスおよび第10世代インテル Core プロセッサーを搭載したSurfaceの新ラインナップを発表」)。当然、Microsoftが「うまくやっている」ことであろう。

気になるコストと製造面

最も気になるのは、この製品のコスト構造だ。製品の複雑度からして従来製品よりは複雑に決まっているが、自前部分以外に外部調達のDRAMパッケージまで重ねている。ご存じの通りDRAM市況は価格変動が激しい。まさかその変動をそのままこの製品に載せるわけにいかないから、供給契約で何らかの安定化が図られるのだと想像する。

一般的に、プロモーション時は末端のお客に近い側が主導権を取りやすいから、Intel主導で決まっていそうだが、いつもそうとは限らない。本格的に競合他社と陣取り合戦をする時期になれば、供給面や価格面でどれだけ手当ができているのか、Intelの本気度が問われる気がする。これまで幾度かあったように、利益率の低いモバイル製品などの優先度を下げるようなことをしていたら期待もしぼむ。それに自前部分も異なるプロセスだ。何かあってどちらかの受給がひっぱくなどするとまずい。ハイブリッドはいいのだが、リスク要素は増えそうだ。昔のIntelならそんなに製造能力を心配しないのだが、「このごろは」である。

こういう「ハイブリッドな」製品を出せるIntelの強みは、設計、製造全てを抱える体制のおかげだが、半面、その限界もその体制にあるように思える。

このごろでこそ、Intelも他社ファブも使っているが、ライバルAMDなどは、元自社ファブだったGF(GlobalFoundries:グローバルファウンドリーズ)を切って、さっさとTSMCへ行ってしまった。Armは実装に直接かかわらないおかげで、自分でやらなくても世界各地のライセンサーがしのぎを削って、コストやスペースファクタなどを勝手に切り詰めている。せっかくの新技術も、コストが割にあわなければ急速な普及は望めまい。そして展開が遅ければすぐにキャッチアップされてしまうだろう。この製品、陰りが見えるIntelにとって、反撃の第一歩となるのか、ずるずるとした退潮の中のアダ花に終わるのか。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

Copyright© Digital Advantage Corp. All Rights Reserved.