日立、10万パラメーターの問題にも対応するスケーラブルな「CMOSアニーリングマシン」を開発 2018年8月にクラウドで公開へ

日立製作所は、交通渋滞の解消や物流コストの低減などをはじめとする実社会の複雑な問題を高速に解く「CMOSアニーリングマシン」を開発。問題規模に応じてスケーラブルに構成でき、CMOSアニーリングチップを25枚接続することで、世界最大規模の10万2400パラメーターの問題に対応できることを実証したという。

日立製作所は2018年6月15日、問題規模に応じてスケーラブルに構成可能な「CMOSアニーリングマシン」を開発したと発表した。交通渋滞の解消やグローバルサプライチェーンの物流コスト低減といった実社会の複雑な問題を高速に解くアニーリングマシンとして実用化を念頭に、2018年8月からパートナー向けにクラウドサービスとして公開し、ソリューションの協創を目指す。

「CMOSアニーリング」は、イジングモデル(磁性体の性質を表す統計力学上のモデル)のふるまいを、半導体のCMOS回路で疑似的に再現する独自技術。同社はこの技術を用いて、量子コンピュータに匹敵する性能を備える新型半導体コンピュータの開発に取り組んでいる。

2015年2月には、2万480パラメーターに対応した専用チップを用いて、約1兆の500乗通りの組み合わせ最適化問題を高速に解く試作機を開発。2016年11月には、プログラム可能な集積回路「FPGA(Field Programmable Gate Array)」を用いた試作機で、計算規模を向上する技術を開発している。

今回、FPGAを実装したCMOSアニーリングチップを25枚接続することで、世界最大規模の10万2400パラメーターの問題に対応でき、これまで拡張が制限されていたアニーリングマシンの性能を、複数チップの接続技術で拡張できることを実証した。

チップ25枚を接続したCMOSアニーリングマシンを用いて、都市の交通渋滞軽減に向けた最短経路探索と、混雑位置を避けるための車両の経路制御をシミュレーションしたところ、従来の25倍の面積に相当する約5キロ四方のエリアで1台当たりの最短経路探索を数ミリ秒で処理できることを確認したという。

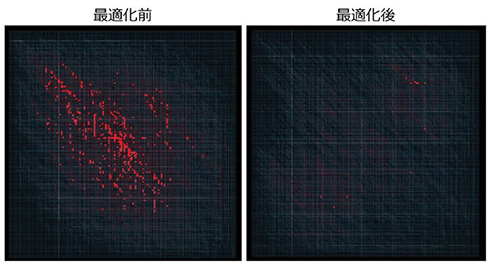

約5キロ四方のエリアにおける都市交通最適化シミュレーションの実行例。縦横160本ずつの道路からなる道路網で2000台の車が交差点の端から端までランダムに移動(左)。移動経路の最適化により、混雑箇所を示す赤い点が減少した(右)

約5キロ四方のエリアにおける都市交通最適化シミュレーションの実行例。縦横160本ずつの道路からなる道路網で2000台の車が交差点の端から端までランダムに移動(左)。移動経路の最適化により、混雑箇所を示す赤い点が減少した(右)なお、チップ間の接続には、高速に変化するパラメーターの値を隣接チップに送受信する必要があり、多数のチップを接続する場合でも通信量が急増しないことが求められる。

これに対して、同社は、各チップ間は境界部分にあたるパラメーターだけを送受信する局所的な通信で十分なことに着目し、隣接するチップ同士でパラメーターの値を絶えず送受信させる「部分結合型」のアーキテクチャを適用することで、全体として一体の大規模なコンピュータとして動作させる形を実現。この構成では「全結合型」と比べて、チップの接続枚数が増えた場合でも1チップ当たりの通信量は増加しないため、省電力かつ低コストでスケーラブルに大規模化することが可能だという。

関連記事

Google、72量子ビットの量子プロセッサ「Bristlecone」で量子超越性を目指す

Google、72量子ビットの量子プロセッサ「Bristlecone」で量子超越性を目指す

Googleが、72量子ビット搭載の「Bristlecone」を発表した。まだエラー率が高いが、このプロセッサで「量子超越性(quantum supremacy)」を達成できるとしている。 富士通が組み合わせ最適化問題を高速で解く「デジタルアニーラ クラウドサービス」を開始

富士通が組み合わせ最適化問題を高速で解く「デジタルアニーラ クラウドサービス」を開始

富士通は、量子現象に着想を得た独自のアーキテクチャで、組み合わせ最適化問題を高速で解く「デジタルアニーラ クラウドサービス」の提供を開始。「創薬の分子類似性検索の高速化」「金融ポートフォリオの最適化」「工場や物流における倉庫内配置の最適化」など、さまざまな用途に向けて展開する。 慶大とIBM、量子コンピュータの研究拠点を開設 実用化に向け、化学・金融の4社が参画

慶大とIBM、量子コンピュータの研究拠点を開設 実用化に向け、化学・金融の4社が参画

慶應義塾大学とIBMが、量子コンピューティングの研究拠点「IBM Q ネットワークハブ」を開設。発足メンバー企業として4社が参画し、化学・金融分野への応用研究や量子アプリの開発などを進める。 5年後に汎用量子コンピュータ登場か、IBM、Google、Microsoftが先陣――NRI、「ITロードマップ 2018年版」を発表

5年後に汎用量子コンピュータ登場か、IBM、Google、Microsoftが先陣――NRI、「ITロードマップ 2018年版」を発表

野村総合研究所(NRI)は、今後のビジネスや社会に影響を及ぼすIT技術について、数年先までの動向をまとめた「ITロードマップ 2018年版」を発表。AI進化の切り札となる「量子コンピュータ」については、2024年度以降に汎用化と予測する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.