第22回 90nmプロセスという21世紀的なるモノ:頭脳放談

半導体の製造プロセスは90nm世代に。各半導体ベンダーがその取り組みを発表する中、早くもIntelはSRAMの製造に成功したという。この意味するところは?

前回の「第21回 変り種メモリはいつ花咲くのか?」で、Intelの新しいメモリを紹介したので、今回は一歩踏み込んで製造プロセスを取り上げたい。2002年3月5日に台湾のファウンダリ(半導体製造会社)のTSMC(Taiwan Semiconductor Manufacturing Company)が、Royal Philips Electronics、STMicroelectronicsと共同で90nmプロセスの開発を行うと発表した(TSMCの「90nmプロセスの共同開発に関するニュースリリース」)。その1週間後の3月12日には、Intelが90nmプロセスの開発に成功したという発表を行っている(Intelの「90nmプロセスに関するニュースリリース」)。というわけで、今回はこのIntelの90nmプロセスについて話をしてみたい。このプロセス技術は、2003年に登場する開発コード名「Prescott(プレスコット)」で呼ばれる次世代のPentium 4製品で採用されるらしい。90nmプロセスという他社がこれから着手しようという技術を、近い将来(来年)に実用化できるという点にIntelの凄さを感じる。

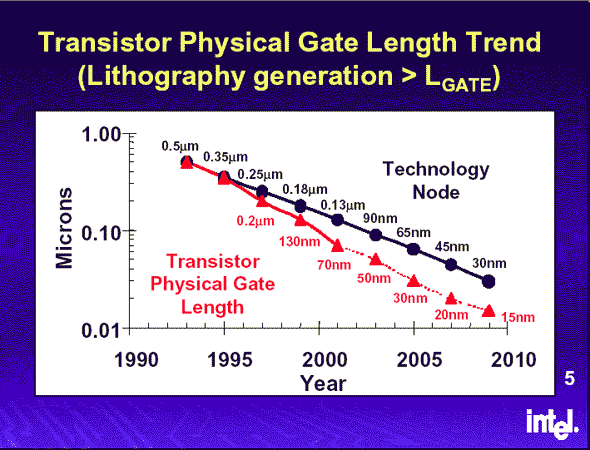

でも「90nm」という表現は、まずもってピンとこない。0.09μmと言い換えるとしっくりくるかもしれない。現在主要な半導体ベンダが先端商品の主力に使っているのが0.18μmで、その次の0.13μmは多くの半導体ベンダではこれから本格化しようというところである。つまり90nmプロセスというと、Intelにすれば次世代になるが、他社の主力製造プロセスからみれば次々世代の発表ということになる。なお、「××μmの製造プロセス」という場合、リソグラフィ(露光装置)*1でなく、実効ゲート長を採用しているベンダもあるので注意していただきたい。0.35μmプロセスのころは、ほとんどの半導体ベンダがリソグラフィと実効ゲート長はほぼ同じ大きさだったが、0.25μmプロセス世代に入ると、リソグラフィに比べて実効ゲート長が短くなっている。そのため、某社で同じ半導体プロセスをX事業部ではリソグラフィで0.25μmプロセスと呼び、Y事業部では実効ゲート長で0.18μmプロセスと呼んでいた、などということも生じるようになっている。Intelの場合は、リソグラフィのサイズで呼んでいる。

*1 シリコン・ウエハに回路パターンを焼き付ける装置または過程。紫外線で回路が描かれたマスクをレンズで縮小投影することで、ウエハ上に回路を印刷する。これにエッチングなどの処理を加えることで、ウエハ上に回路が形成される。この回路を縮小投影する能力によって、回路の線幅が決まってくる。

ともかく「ナノメートル(nm)といういい方が21世紀だ」と思う。半導体、特にMOSテクノロジの歴史を見れば、2桁μmから始まって、ここ10年ほどはサブ・ミクロンになり「コンマ××」と呼ばれて久しいが、さすがにコンマの後にまた0が続くと呼びにくくなってくる。これからは学会発表に限らず、「ナノ」が幅を利かせるようになるかもしれない。

なぜ6トランジスタのSRAMなの?

さてIntelの発表だが、今回はプレゼンテーション資料のタイトルから解説していきたい。「Intel's Next-Generation Logic Process Proven With World-Record Memory Chip(Intelが世界記録のメモリ・チップで次世代ロジック・プロセスを実証)」である。ちょっと変なことに気付く。次世代の「ロジック」プロセス(ロジック:論理回路)についての発表なのに、それは世界記録の「メモリ・チップ」で検証されたと書いてある。このタイトルで変に感じないのは、たぶん半導体業界の人だけだろう。「当然! このメモリとは6トランジスタのSRAMのことだろう」という理解である。多分、そういう人には、「0.09μmのリソグラフィで6トランジスタのセル・サイズが1μm2」といえばOKだ。この先は読まなくてよい。

90nmプロセスに関するIntelのプレゼンテーション資料

90nmプロセスに関するIntelのプレゼンテーション資料タイトルは、「Intel's Next-Generation Logic Process Proven With World-Record Memory Chip」となっており、メモリ・チップでロジック・プロセスの検証を行ったことを示している。

まず、ロジックのプロセスと(普通でいう)メモリのプロセスの違いだが、メモリの中でもDRAMのプロセスは乖離がはなはだしい。DRAMはロジックより微細化が進んでいるといえばそうなのだが、キャパシタンス(静電容量)を確保するために縦方向(厚み方向)への伸張が著しい、いまや深い谷と山の世界になっている。この点、配線層の数まで含めて水平方向の集積度を狙うロジックのプロセスとは大きく異なる。次にフラッシュメモリなどのEPROM系の製造プロセスやアナログ系の製造プロセスであるが、これらはどれもロジック系にない特殊な層を持つのを特徴としている。もちろんDRAMやフラッシュメモリ、アナログとロジックを混載するようなこともあるので、多用途な製造プロセスもあるだろう。しかし通常、ロジック・プロセスといえば、ともかく論理回路を大量に集積するためのプロセスで、DRAMのような縦構造や特殊な層は含まないのが前提となる。多用途な混載は、ある意味オーバーヘッドになって集積度と速度の両方とも先端は追求できないからだ。つまりDRAMやフラッシュメモリではロジックの代表にはならないのだ。

ここで指標になるのが6トランジスタで1bitの記憶素子を構成するSRAMセルだ。論理回路という場合、NORやNANDといった論理ゲートを中心に構成されるが、論理ゲートを構成するトランジスタの大きさには絶対値での指標がないため、回路の構成に依存する。その点、6トランジスタのSRAMセルはロジック・プロセスの「素のまま」で構成できる高速な記憶素子で、キャッシュなどとしてロジック製品でも大量に利用するセル構造である。また速度と面積ともに「絶対値」で比較しやすいので、ロジック・プロセスの指標としてよく採用されるのだ。実際、最先端のロジック製品のチップは、下手をすると面積のほとんどがSRAMである。キャッシュやバッファなど、いろいろ名称はあるが、高速になればなるほどいわゆるロジック部分よりメモリ部分が大量に必要になるのは、汎用プロセッサに限らない。そういうわけで、各社ともロジック・プロセスの実力を表す場合の1つの指標として、この6トランジスタのSRAMのサイズを使う場合が多い。なお、6トランジスタ以下のトランジスタ数で構成するSRAM、例えば4トランジスタといったものもあるが、多くはSRAM専用の製造プロセスを用いるので、ロジック・プロセスの指標にはならない。また、1トランジスタのSRAMというのは、SRAMの皮をかぶったDRAM(ただしDRAMプロセスではなく、ロジックで可能)なので指標にはしない。

今回のIntelの発表は、この90nmの製造プロセスで1μm2の領域に6トランジスタを押し込んで1bitを構成できた、というものである。これがどれくらい凄いか? 発表では0.13μmプロセスと比べて半分の面積だといっている。現状、業界の主力である0.18μmプロセスと比べると、当然ながら半分以下の面積ということになる。同じ0.18μmプロセスといっても、各社によりセル・サイズにはいろいろ差がある中で、一番小さな方と比べて4分の1くらいだろう。これは、むちゃくちゃ小さいといえる。当然、同じ容量なら4分の1の面積(半導体は不動産同様、面積商売だということを思い出してもらいたい)、ざっくり4分の1の価格で製造できることになる(「第13回 300mmウエハは2倍お得」参照のこと)。

次にこのプロセスの名前だが「P1262」という。各社ともプロセス名は分かりにくいものが多い中で、Intelのネーミングは比較的分かりやすく、最初の数字はウエハのインチ・サイズである。P4××ならば4インチ、P8××ならば8インチという具合だったのだが、2001年になって12インチ(300mm)ウエハが投入されたので2桁になってP12××と呼称されている。××の部分は、プロセス系列を示す追番になっているようだ。昔はともかく、ここしばらくは2年おきに+2される番号を使っているらしい。

| プロセス名 | 製造開始年 | リソグラフィ | 実効ゲート長 | 主な利用製品 |

|---|---|---|---|---|

| P854 | 1995年 | 0.35μm | 0.35μm | MMX Pentium(P55C)/Pentium II(Klamath) |

| P856 | 1997年 | 0.25μm | 0.20μm | Pentium II(Deschutes)/Pentium III(Katmai) |

| P858 | 1999年 | 0.18μm | 0.13μm | Pentium III(Coppermine)/Pentium 4(Willamette) |

| P×60 | 2001年 | 0.13μm | < 70nm | Pentium 4(Northwood) |

| P1262 | 2003年 | 90nm | < 50nm | − |

| P1264 | 2005年 | 65nm | < 35nm | − |

| Intelのプロセスの流れ | ||||

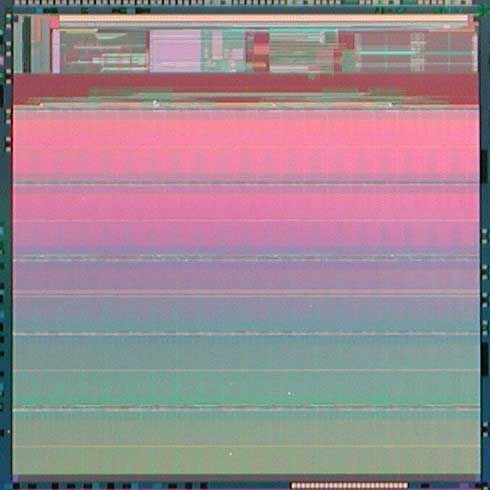

90nmプロセスで製造したSRAM

90nmプロセスで製造したSRAM10.1mm(横)×10.8mm(縦)の大きさで52Mbit SRAMを実現している。なぜ52Mbitという中途半端な容量なのかという質問には、あくまで実証テストで作成したものであるため意味はない、という答えが返ってきた。単にチップ・サイズを1cm2程度に収めたら、52Mbitになったというだけなのかもしれない。

ウエハのインチ・サイズが大きいのは、金をかけた工場を持っている証拠である。半導体製造装置の多くは特定のウエハ・サイズに対応できるように設計されている。そして非常に高価な12インチ用の装置を並べて工場を作ることができるというのは、何千億円もの設備投資をしている/できるという証明でもある。また、「12インチ=8インチ×2.25倍の面積」であるから、同じ枚数のウエハを処理できたとすれば、2.25倍のチップ数を作れるという量の証明でもある。たかだか「12」という数字であるが、他社が感じる圧迫感はどの程度のものなのだろうか。

こういう発表をするIntelの意図であるが、これは当然、すぐれた自社技術の誇示により株価そのほかへの好影響を考えてのことであるのはいうまでもないだろう。だが、Intel創業者のゴードン・ムーア(Gordon Moore)博士の指摘ではあるものの、ことさらにムーアの法則を持ち出し、強調しているのは、半導体プロセス・テクノロジが壁にぶち当たりつつあるという意見を当面否定したい、あるいは、まだそれは先のことだと先送りしたい意図が透けて見えるように思うのは、うがち過ぎだろうか。確かに90nmの製造プロセスは、SRAMを実際に作って見せたことで機能を証明した。しかし、信頼性やそのほか量産にいたるまでにはまだ仕事が残っている。そしてその次もいける、という保証ができたわけではない。その次に進むためのハードルを1つ越えたというだけのことである。Intelも手放しで楽観していないことは、過去30年の研究開発と投資でムーアの法則を自ら実現してきたといいつつ、プレゼンテーション資料の中には「at least through end of this decade(少なくとも次の10年は法則どおりに続く)」という表現に微妙に表れているように感じられる。Intelをもってしても、この先の微細化はどんどん苦しさが増していく、と覚悟はしているのだろう。

■関連リンク

- 90nmプロセスの共同開発に関するニュースリリース[英語](TSMC)

- 90nmプロセスに関するニュースリリース(インテル)

- プロセス技術に関する技術情報ページ[英語](Intel)

- 90nmプロセスに関するプレゼンテーション資料[英語][PDF](Intel)

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.

リソグラフィと実効ゲート長の関係

リソグラフィと実効ゲート長の関係 Intelが実証に用いた6トランジスタのSRAMセル

Intelが実証に用いた6トランジスタのSRAMセル