第102回 「Core i7」の面を見れば……:頭脳放談

最新プロセッサ「Core i7」が登場。ダイのレイアウトを眺めると、機能がブロック化されて、デザインが美しい。次は対称にコピーして8コア化か?

「面(つら)を見れば素性が分かる」と、これは大昔に当時の上司から聞いた言葉である。業界話なので、「面」といっても人の美醜や性格をどうこう、というわけではなく、「面=半導体チップのレイアウト」の話だ。世にはびこるか否かは人の面相と同様、必ずしも美醜によらない。しかし設計という行為は、常に「相反する何かと何かの釣り合いを取る(トレードオフ)」という行為の積み重ねである。そのため、美しいレイアウトというものは「ブレ」のない設計の結果であることが多い。「面を見れば……」という言葉は、そんな経験を反映していたのだ、といまになって思う。

最近のマルチコア・プロセッサのレイアウトはまずは美しいものが多い。歴史的にいえばこれほど「美男美女」ぞろいのレイアウトの多い時代はなかったのではないだろうか。自分のことは棚に上げて批評するならば、初期の時代のプロセッサは、いろいろな試行錯誤を積み重ねた手作り感があり「個性派」ではあるが整ってはいなかった。それが32bit化する前後からきれいにデータ・パスとコントロール・パスが分かれ、まさに情報の流れが目に見えるような整ったレイアウトになってくる。それがスーパースカラ化、高速化の競争の中で複雑かつ厚化粧な感じになり、さらにマルチコア化とともにその複雑さが奥へ引っ込んで、シンメトリーな美しさが前面に出てきている。

美しいCore i7のレイアウト

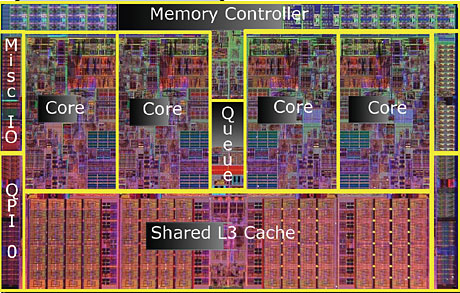

今回、発表になったIntelの「Core i7」プロセッサ(開発コード名Nehalem:ネハレム)は、そんな美しいレイアウトの中でもひときわ対称性が際立つ美しいチップである。まぁ、公開写真はお化粧のための彩色がされているのだろうから、見た目が美しいのはもちろんだが、ほれぼれする対称性である。中心の対称軸を挟んで2個ずつのコアが左右に配置されており、合計でクアッドコア(4コア)となっている。コア側の長辺にメモリ・コントローラが並んでおり、反対側にはこれまた中心軸に対称に8Mbytesの3次キャッシュが配置されている。よく見れば、「組」になって左右に配置されているように見える2個のコアであるが、「組」の中では「フリップ(反転)」配置されておらず、あくまで中心の対称軸を向いて同方向で配置されている。「フリップ」関係はすべて唯一の中央対称軸に対してである。行きかう「データやコード」が中央対称軸を中心に双方に「振り分け」られていくのが目に見えるようなレイアウトといってよい。

この対称性はクアッドコアだからともいえるが、メモリ階層にも要因があるように思われる。1次キャッシュはコードとデータを分離している。これはプロセッサのパイプラインを考えれば必然だが、サイズは32Kbytesずつでシンメトリーである。

2次キャッシュは、実行するプログラムによってコードとデータの必要量は大きく変動するが、コードとデータが共用の256Kbytesである。1次キャッシュの合計容量の4倍ととらえることもできる。だが、例えばデータ主体のプログラムであれば、32Kbytesの1次データ・キャッシュの8倍まで、2次キャッシュにデータが置けると考えてもよいのだ。そして、2次キャッシュまでが各コア独立の部分である。この下に全コアで共有する3次キャッシュが8Mbytes実装されている。各コアの2次キャッシュを合計した容量が256Kbytes×4個で1Mbytesだから、サイズ的にいえば3次キャッシュも2次キャッシュの8倍になっている。

3次キャッシュでは、各コアの「スヌーピング(データの整合性を保つ動作)」を最小に抑える、ということが最大の眼目になっている。そのためか、コアの幅に合わせて大きく4ブロックに配置されている3次キャッシュだが、それぞれの中に少なくとも8行4列の構造が読み取れる。各ブロック2Mbytesに対して、32分割だから、小さな構造はそれぞれ64Kbytesである。各プロセッサでシェアされるので、整合性と速度を両立させるために、小さな構造で読み書きを並行管理することで、オーバーヘッドを最小化しているものと思われる。

さらに、高速な外部主記憶メモリへの「チャネル」もプロセッサが直接管理するというのが、このプロセッサの売りの1つでもある。階層メモリ構造のサポートは徹底している。しかし、さすがに外部メモリ・スロットについては対称性を押し付けることまではしていない。全部で3チャネルあるメイン・メモリへのチャネルは、それぞれ2個のスロットをサポートしているが、異なるサイズのメモリ・モジュールの共存を許している。その場合、内部のロジックで物理チャネルとは異なる論理的なメモリの順序の割り付けを行うようだ。これにより可能な限り、多くのチャネルをインターリーブして使える。

しかし、このプロセッサのメモリ階層へのコダワリを見てしまうと、異なるサイズのメモリ・モジュールを偏ったスロットに入れるような使い方は、「間違っている!」といってもよいかもしれない。同じサイズのメモリ・モジュールで全スロットを埋め尽くすべきだろう。何せ「メモリへのボトルネックを作らない」のがマルチプロセッサの金科玉条であり、このプロセッサは忠実にそこを押さえているのだから、そこは汲み取ってやりたい。

なぜかよみがえるメインフレーム時代の記憶

「デスクトップ」向けの主力プロセッサとして登場してきたCore i7の「面」を見ながら、年寄りはふと「面」の話を聞いた若かったころを思い出す。当時、仮想計算機OSが登場しており、ホストOSの下で複数のゲストOSが走っていた(それでまさにプロセッサのレイアウトの検証などやっていた)。マルチプロセッサ化も進んでおり、2/4/8みたいなプロセッサ数の構成によってシリーズ機種の型番が付いていたはずだ。また、その前の時代には、「ビット数(といってもアドレスのビット幅)」が足らなくなったために直面していた壁が、「拡張アーキテクチャ」などというものが導入されたおかげで取り除かれ、メモリ容量も巨大化の一方だった。これは当時「メインフレーム」といわれていたもののおぼろげな記憶である。また当時「パーソナル・コンピュータ」などというものは「メインフレーム」に比べたら「玩具」のようなものだと思われていたし、実際、その当時のレベルで比べればそのとおりの差があった。しかし、その後は歴史の示すとおりだ。

さて、いまや「デスクトップ・コンピュータ」を見れば、当時の「メインフレーム」をはるかにしのぐ性能ではあるものの、しかし見える状況といえば、なぜか「メインフレーム」が「頂点」に達したころの状況と似通っていること、偶然か必然か。この先、どちらへ進むのか。「X軸で『フリップ』して8コアにする」こと自体は、Core i7のレイアウトを見れば「そういう配慮もされていて、とても簡単そう」に見えるし、それはそれで対称性が増して美しくはあるのだが、はっきりいって「芸」がない。そろそろ本格的な「パラダイム」変更が必要に思えるのだが……。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.