第30回 親亀に小亀と半導体チップを重ねてみれば:頭脳放談

携帯電話が小さくなった背景には、半導体チップのパッケージ技術がある。今回は「スタックドパッケージ」と呼ばれる、その技術について話そう。

「第25回 DRAMの覇者Micronの次の一手」で少し触れた「スタックド・パッケージ」を今回取り上げてみたい。そんなものは知らない、という人も多いかもしれないが、そういうほとんどの人が実はすでに「持っている」ものなのである。

複数のチップを1つにまとめたい?

「スタックド・パッケージ」というからには、何かをスタック(積み重ね)しているわけだ。何をスタックするのかといえば、半導体チップなのである。複数のチップを積み重ねるのでスタックドという名がついたのだ。英語的に正確を期せば「スタックド・マルチチップ・パッケージ」というべきであろう。似たような言葉で「マルチチップ・モジュール(Multi-chip Module:MCM)なら聞いたことがある、という人もいるかもしれない。

MCMは、複数のチップを配線まで含めて1つのパッケージに実装したものだ。各チップからの発熱なども考慮されて設計されている。こうしたことから、複数のチップで構成されているといっても、外見は少し大きな1つのチップにしか見えない。組み合わせる複数のチップは、MOSとバイポーラといったように製造プロセスが異なっていても構わない。メモリとロジックといった組み合わせが一般的だが、モジュール全体として機能を実現するようにしている。歴史的にはかなり古くから大型汎用機などで使われてきた技術だ。当時の「マルチチップ」技術は、限られた集積度のチップを接続する場合、それぞれのチップをパッケージングしてから基板で接続するより、集積度の高いモジュールにすることで配線遅延(電気信号が配線を伝搬していく際の時間的な遅れ)を抑え、高速動作と放熱を確保するという面が強かった。当然のことながら値段もベラボウに高くてコンシューマ向け製品に使えるものではなかった。MCMで有名な製品というと、IntelのPentium Proが挙げられる。Pentium Proは、プロセッサ・コアと2次キャッシュ(SRAM)をMCMで1パッケージ化したのだが、やはり価格が高くなってしまい、あまり多くの数は出荷されなかったようだ。

この手の技術は進歩し、徐々に値段も下がっていたのだが、局面が一転し、一般消費者向け製品に大量に使われるようになったのは携帯電話のおかげである。ほとんどの人が持っているといったのはそのためだ。とはいえ、かつての古い技術とは断絶があり、ともかく実装面積を小さく、かつ安く、というニーズに応えているのがスタックド・パッケージだ。最近の携帯電話の中身を見てみれば、多分、複数のスタックド・パッケージが搭載されているはずだ。それも7〜8mm角といった小さな外形、1mm程度の薄さで実装されている。これは、スタックド・パッケージのほとんどが、チップ・サイズ・パッケージ(Chip Size Package:CSP)と呼ぶ、ほぼ半導体チップ(ダイ)と同じサイズのパッケージを採用しているためだ。そのため、スタックド・チップ・サイズ・パッケージと呼ぶことも多い。携帯電話の小型軽量化を可能にした技術のうちの1つである。

積み重ねるのもいいものだ

携帯電話に使われている代表的なチップ・サイズ・パッケージ品は、SRAMとフラッシュメモリを積み重ねた「コンボ・メモリ」などと称されるメモリ製品である。メモリを用いた回路の回路図を見たことあれば分かるのだが、どのメモリにもデータ・バスやアドレス・バスなどの同じ信号が接続され、メモリごとに異なる信号線は実は数本しかない。つまり、各メモリに共通の配線が、回路基板上の面積を大きく占有しているわけだ。これを見たら実装面積を何とか小さくしたいと考えている携帯電話の設計者が「重ねたい」と思うのは無理ない欲求である。この重ねるという発想はそれほど新しいものではない。IBM PC/AT用のメモリなどでも、DIP(Dual Inline Package)のDRAMを2個重ねて、「スタックド」的な実装をしているものもあったほどだ。もちろん、これはパッケージ化されたものを重ねているので、ここで話をしているスタックド・パッケージとは異なる。

現在では、SRAMとフラッシュメモリを2個重ねる以外にも、容量によってSRAMを1個にフラッシュメモリを2個、3個と重ねるといったものもある。ほかにもインテルが2002年10月15日に発表した「PXA262」のように、プロセッサとフラッシュメモリといった組み合わせもある。しかし、いぜんとして主流はメモリ製品である。インテルの例のようにロジック製品とメモリ製品のスタックド・パッケージの例もあるが、種類、数量ともにメモリ製品が圧倒的に多い。

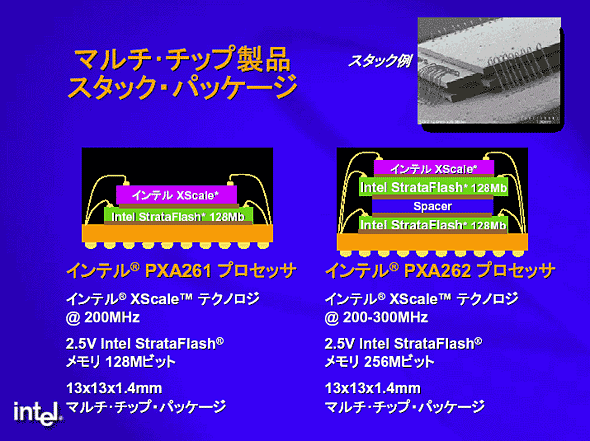

スタックド・パッケージを採用したインテルの「PXA261」「PXA262」の例

スタックド・パッケージを採用したインテルの「PXA261」「PXA262」の例インテルの携帯電話向けプロセッサ「PXA261」「PXA262」では、組み込み向けプロセッサの「XScal」eとフラッシュメモリの「StrataFlash」をスタックド・パッケージ化した。これにより、携帯電話における実装面積がさらに小さくできるという(インテルの発表資料より)。

前述のとおり、共通の配線(端子)が多いメモリ同士を重ねるのは自然だ。一方、多様な端子を多数持つロジック品を入れると、端子数的にも機能的にも格段に複雑になるので、出荷試験などの難しさが増すことになる。また、SRAMとフラッシュメモリなどメモリ製品は、それぞれの製造プロセスが極端に違うので、この両方を混載してワンチップ化するのはそもそも難しい。スタックド・パッケージ化するのは当然の帰結だ。

しかし、ロジックとSRAM、ロジックとフラッシュメモリ、ロジックとDRAMなどという組み合わせでは、ワンチップ化も可能である。ワンチップにするかスタックド・パッケージにするかは、微妙な選択となる。ロジック製品でありながら、スタックド・パッケージ化したいという場合は、ロジックに複数種類のメモリを重ねるような集積が多くなる。比較的安いメモリを2〜3個重ねているうちは、結線やパッケージの問題で収量が悪くても損害は小さいが、これにマイクロプロセッサといった価格の高いものが含まれるようになると痛手が大きくなる。それなりの必然と準備がないと踏み出せないのである。

スタックド・パッケージで指先に載る製品が生まれる?

スタックド・パッケージ自体には、メーカーやパッケージ形状によって何種類もの構造がある。一般的なのは、大きいICチップから小さいICチップへと順番に重ねていき、それぞれのICチップの四辺にあるボンディング・パッド(結線用のエリア)にワイヤー・ボンディングしていく、という構造だ。段数が多いことを除けば、既存技術の延長といえる。それ以外にも下層のICチップは下向きにパッケージ基板に実装することで、ワイヤーを使わずに接続し、2個目は上向きに実装してこちらはワイヤー・ボンディングを行うという方法、フレキシブルな基板にチップを接続しておいて基板を折り畳んで重ねる方法など、多種多様である。いずれにせよ、携帯電話などでは超薄にしないとならないので、接続するチップ(実際にはウエハの状態で削る)は普通より薄いものが使われる。

異なる製造プロセスで作られたICチップを重ねられるというスタックド・パッケージの利点は、ビジネス的にも面白い局面を作り出している。製造会社の異なるICチップを重ねて1個にするというビジネス形態である。それぞれ半導体会社によって得手不得手があるから、各社得意のものをかき集めて重ねて、見掛け上1個の製品にするということができる。とても面白く、可能性もあると思っているのだが、半導体ベンダからチップで出荷してもらう必要があるため、組み合わせるICチップを揃えるのがなかなか難しい。また、パッケージが小さいだけに放熱も問題で、携帯電話向けチップのように消費電力が小さなものはできるが、PC向けICチップとなると当面は不可能だ。

Tesseraが開発した「フォールド・スタックド・パッケージ」

Tesseraが開発した「フォールド・スタックド・パッケージ」パッケージ・ベンダのTesseraが開発したスタックド・パッケージの一種。配線済みのテープ基板にチップを実装し、それを折り畳むことでスタックするというものだ。

近頃では、5段スタックといったものも現れており、そろそろ単純なスタックド・パッケージでは携帯電話の集積度向上には不十分になってきそうである。そこで、各社はパッケージの上にさらにパッケージを重ねるという形の「パッケージ・オン・パッケージ」といった製品もラインアップして始めている。これなどは昔のDIPメモリを重ねていたのと同じ発想である。もちろん、今回の場合は、重ねたパッケージ自体もICチップをスタックド・パッケージ化しているものだ。ICの集積度アップに加え、このような実装技術でも加速が加わり、真の意味で指先に載る応用製品が現れるのもそう遠くなさそうである。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.