第33回 ボタン電池で5年間駆動可能な携帯電話への道?:頭脳放談

半導体業界にとって「低消費電力化」は長年の課題である。そこで、低消費電力化の必要性と、省電力化の最新設計手法について解説する。

2003年もISSCC(IEEE International Solid-State Circuits Conference:半導体関連の国際会議)の季節になった。今年は2月10日から米国カリフォルニア州サンフランシスコで開催され、多くの論文発表があったようだ。こうした大きな会議があると、担当編集者からは「ISSCCで話題になっているこれこれの件をテーマに」というリクエストがくる。どうも、今年はこれで決まりという題材がなかったのか、「省電力の話当たりで何か」という依頼になったようだ。「話当たり」という言葉には、「この発表」という特定はないけれど、「低消費電力」に関する話題が目立っていた、という背景があるのだろう。低消費電力化は、今年に限らず長年の課題で、当分トピックでもあり続けるネタだ。そこで、今回は少々リクエストを拡大解釈して、低消費電力のトレンドを取り上げることにした。

複数の動作電圧を使い分けて低消費電力化

低消費電力化が急務といわれて久しい。何せ集積度が急速に高まっている上に、動作周波数が高くなっているから、低消費電力化しないとメルトダウンを起こしてしまう。Intelのパトリック・ゲルシンガー(Patrick Gelsinger)副社長(当時。現在は上級副社長)は、2001年のISSCCの講演で「1平方cm当たりの消費電力が製造プロセスの微細化にともなって急速に上昇しており、この傾向を放置しておくと将来プロセッサでは単位面積当たりの発熱量が原子炉やロケット・ノズル並になる」と述べている。確かにハイエンドのプロセッサでは、こうした理由から低消費電力化が叫ばれているようだ。

だが、多くの半導体製品においては、携帯電話に引っ張られて、業界全体がバッテリ応用に向かっているから、という方が本筋だろう。モバイルとか、ユビキタスとか、ともかく持ち運べる(つまりはバッテリ駆動)製品に注目が集まっている。少しでも長い時間、バッテリで駆動できることが差別化のポイントにもなる。そのためには、CMOSの原理に従い、「ともかくクロックを止める」というのが金科玉条なのだが、もはやそれだけでは十分ではなくなっている。

今年のISSCCで真正面から低消費電力化技術を取り上げたのが、日立製作所だ。レベル変換回路を使って低電圧低速回路と高電圧高速回路を接続するというアイデアを採用した試作品と、マルチプロセッサ向けの低消費電力化技術を発表している(日立製作所の「二電源方式回路技術の開発について」「マルチプロセッサに対応した低消費電力回路技術の開発について」)。

実際にLSIの設計をしたことのある人はシミジミと分かるのだが、チップ内で複数の電源を使い分けるのは非常に面倒な上に、いろいろな面でオーバーヘッドが大きくなる行為でもある。電圧が異なる部分ごとに仕切らなければならないので、必然的に面積が広くなり、その分価格が高くなる。また、レベル変換回路を介するので信号も遅延する、ということで大変なのである。また、各電源を個別に上げたり落としたりして制御しようなどと野望を抱くのはいいけれど、万が一、電源の投入順序を間違えるとラッチアップ*1を起こして素子が壊れてしまう。こんなことは、やらないで済むならやめたいところだ。

*1 トランジスタ間で素子が通電状態になり、過大な電流が流れつづける現象のこと。いったんラッチアップが起きると、電源を切るか、電圧を下げないと、元の状態に戻らない。そのままの状態に放置しておくと、過大電流によって配線が切れるなどして、素子が破壊されてしまう。

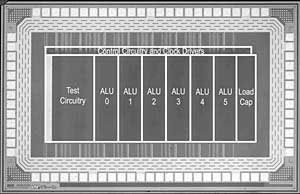

ともかく、可能な限り低消費電力にしようと思えば、低電圧化は避けられない。単に動作周波数を落としただけでは、動作が遅くなるか、止まってしまうだけだからだ。でもやたらと全体を低電圧にすると、上限の動作速度が上げられなかったり、外部回路とのインターフェイスに困ったりすることになる。一般的にトランジスタは、動作電圧を低くすると動作速度が遅くなってしまう。また、メモリなどの動作電圧は決まっているので、ヘタにインターフェイス部分まで電圧を低くしてしまうと、今度はその接続部分に工夫が必要になってくる。そのため、電源を分離して低電圧動作のブロックを作るというのは、低消費電力化には必須の技法なのだ。もちろん、微細プロセスを使うためには避けて通れない定番手法でもある。日立製作所のこの技術を使って、簡単にこれらの問題が解決できるとすれば、実装上はとても素晴らしい。設計者がこれに慣れたら、日立製作所以外ではSoC(System on Chip)を作りたくなくなるかもしれない。ただ、いまのところALU(算術論理演算回路)にフォーカスしてデータを取ったような段階なので、設計者がすぐに使わせろといっても駄目だろう。今後の展開に期待したい、というオザナリなコメントを付けておく。

電圧と周波数は「ビミョーな関係」を調整する技術

日立製作所が発表した低消費電力化技術のうち、マルチプロセッサの方は、いまや各社定番と化した感のある、電源電圧と動作周波数を動作時に「最適な」ポイントに再設定するという技術をベースにしたものだ。日立製作所は、この技術を「ユニバーサルコントロール」と呼んでおり、これを今回はマルチプロセッサ向けに巧妙にした、という発表であった。テーブルを使って「学習」するのがポイントのようだ。

電圧と周波数は「ビミョーな関係」なので、その制御は巧妙であればあるだけよさそうだ。ただ、マルチプロセッサ向けに巧妙にする前に、まだいろいろと実施できることはありそうだが、どうか? まぁ、IntelはXScaleで、「クラッチを入れ替えるのにエンジンを切る」とでもたとえられるような、かなり荒っぽい制御を採用しているのに比べれば、日立製作所の技術はかなりスマートといえるだろう。とはいえ、Transmetaも繊細な制御をしているし、鼻の利く点では抜け目ないARMは、Intelなどとは差別化すべく、技巧を凝らした電圧とクロック周波数の制御を開発中なようだ。

だが、どれも基本は低消費電力にするために、「その周波数を確保できる最低の電源電圧を使う」、あるいは逆に「その低い電源電圧で確保できる最高の周波数を設定し、適宜、電圧と周波数条件を切り替えて動作する」というもので、手法は同じだ。極論すれば、電池駆動の4bitマイコンなどでは20年も前からやってきたことの延長である。その手のマイコンは、ボタン電池1個で何年も動作しなければならないから、必要なときに一瞬だけ高速動作し、普通は非常に低速で動作し続ける。内部にレギュレータ(変圧装置)を持っていて、極端に切り詰めた電源電圧でひっそりと動作する。昨今の32bit、特にどんなプログラムが走るか分からない汎用プロセッサに比べて、4bitマイコンのプログラムは、超が付くくらい単純なので、走ったり止まったりする制御は確かに簡単だ。複雑なアルゴリズムやOSを使う32bitプロセッサとはそのへんが違うが、根本原理は変わらない。4bitマイコンの中には、「電池が持ちすぎる」というクレームをつけるユーザーがいたという伝説があるくらい徹底したものもある。この際、何かパラダイムを変革するような技術が欲しいではないか!

3つの低電圧化の新技術候補

勝手な意見でいくつかそのような技術の候補を挙げてみたい。第1は「非同期設計」である。現在のSoCのほとんどがRTL*2で設計され、同期設計向きの論理合成ツールを使って作られている。このような設計環境では、「非同期な設計はしないように」と教育されている。非同期というのは、過去の亡霊というかタブーのように思われているのだが、実はRTLで設計可能で、論理合成ツールも利用できる新しい非同期設計の研究が進みつつあるのだ。

*2 Register Transfer Level。ハードウェア記述言語によるロジック回路生成が可能な程度の抽象度での設計。

そこではクロック同期のフリップフロップ回路の代わりに、データを要求、到着、と順次伝えていく非同期な記憶素子が中心になる。クロックがないために、クロックに同期して一度にガツンと電流が流れることがない(クロックに同期していると、一度に多くの素子が動作するので、当然ながら電流も多く流れることになる)。ピークを作らず、ゆるゆると電流が流れるので、消費電力の面では相当有利になる。それに同期設計では、消費電力を抑えるために、ある時点で不要な回路にクロックを供給しないようにする必要があり、これに「ゲーテッド・クロック」というものを多用する。これもいっぱい作ってしまうと、設計上で結構厄介なことになるのだが、非同期ならばこんなものも不要になる。非同期では、原理的に必要なところしか動かないからだ。また、電圧が変動して遅延率が変わっても、それなりに動作するので、先ほどの電圧とクロック周波数の微妙かつ巧妙な制御などは本質的に無用である。問題は高度に進化した同期設計向けのツールと、それに対応した設計手法に設計者がみんな慣れているので、これをひっくりかえすのが並大抵なことではない、ということであろうか。

第2は少し意外かもしれない。「第31回 次世代不揮発メモリが夢見る明るい未来」で少し触れた、「リコンフィギャラブル」技術をうまく使えたら可能性がありそうだと思っている。動的に必要な回路を構成する技術である「リコンフィギャラブル」は、大規模な回路をそれより規模の小さい回路で置き換えられる可能性がある。すでにソニーが、携帯型MDプレイヤーの「NW-MS70D」で実用化しており、従来の汎用DSPの1/4の低消費電力化を実現したとしている。しかし、回路ひとつひとつの動作頻度は高いので、リコンフィギャラブル化するためのオーバーヘッドが大きすぎると、やぶ蛇になってしまう。

第3はアルゴリズム的な切り口で、遺伝的アルゴリズム(GA)というやつを挙げておきたい。遺伝子が進化するように、アルゴリズムやそれを元にした回路動作が進化していくものだ。ようやく一部で実用化が進み始めている。これもうまく使えば回路規模の割に性能が格段によいものが開発できそうだ。低消費電力化に限っても、電源制御は実行するプログラムの挙動に依存するのでなかなか予測が難しく、最適な制御は困難だが、GAを元にすると、より巧妙にオートマチック化できるのではないかと思う。

今回は3つばかり可能性を挙げたが、もちろんこれだけではないだろう。低消費電力化でも激しい競争が続いているので、正攻法あり、奇天烈なものあり、いろいろ出てくるに違いない。だが、まだ当分の間、携帯電話の充電はやっぱり必須だろう。4bitマイコンのように、5年たったけれども動いていたとはいかないと予想する。いくら低消費電力化技術が開発されても、音声から画像、画像から動画と、携帯電話がカバーする領域は、技術開発以上の速度で広がり、それを支える集積度も速度もウナギ上りだからだ。いまのところ携帯電話ベンダは、電池寿命をいまよりも短くせずに、どれだけ機能を詰め込めるか、という勝負をしている。考えると、これってエコじゃないなぁ。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.

日立製作所が試作したニ電源方式の64bit ALU

日立製作所が試作したニ電源方式の64bit ALU