第19回 Intelが示したテラ・ヘルツへの夢、そして現実:頭脳放談

Intelが開発した新しいトランジスタ「TeraHertzトランジスタ」は2.63THz(テラヘルツ)のスイッチング速度を実現する。このトランジスタ発表の意味を探る。

前回「第18回 今度の半導体不況はいつもと違う?」で、これからの半導体はお先真っ暗みたいな話を書いたら、同時期にIntelからはまだまだ「ムーアの法則*1」どおりに半導体は進歩するのだという強烈なニュース・リリースが出された。「Intel TeraHertz」と呼ぶ新しいトランジスタの発表である(Intelの「TeraHertzトランジスタに関するニュースリリース」)。このトランジスタの構造は、開発研究者の間では「depleted substrate transistor(完全空乏型基板トランジスタ*2)」と呼ばれるものだが、これではいかにも技術的すぎて、一般受けする名称ではない。そのためか、例によってIntelは、「Intel TeraHertz」というマーケティング主導のネーミングを付けずにはいられなかったようだ。実用化にはまだはるかに遠い技術だが、こうして先々のロードマップを常に提示することで、これからも業界をリードし続けるという意思の表れとも取れる。また、一部でまん延している「お先真っ暗」論議を吹き飛ばすという意図も見え見えのニュース・リリースでもあるので、今回はこの新トランジスタ構造を取り上げることにする。専門家を差し置いてロジック屋(回路設計屋)がトランジスタや製造プロセスを論じる後ろめたさがあるけれど、勘弁してもらいたい。

*1 Intel創設者の1人、ゴードン・ムーア博士が唱えた経験則。マイクロプロセッサに集積されるトランジスタの数は18カ月ごとに2倍になるというもの。

*2 絶縁層が50nm以下で基板領域がすべて空乏(電荷を運ぶキャリアが存在していない領域のこと)化しているものを完全空乏型、100nm以上で基板領域に空乏化されていない領域を持つものを部分空乏型と呼ぶ。

TeraHertzは最新トレンド

TeraHertzは、確かに超最先端のトランジスタである。ゲート長は15nm。いま、多くの会社で最先端の商用主力プロセスというと0.18μm、そろそろ0.13μmになろうかというところだ。両者の単位をそろえてみると、15nm=0.015μmであるからその微細さ加減が分かるだろう。このように微細化していくということは、高速なスイッチング動作につながる。その速さは2.63THz(テラ・ヘルツ)だそうだ。これもよく使う単位にそろえれば2630GHzとなる。トランジスタのスイッチング速度がそのままプロセッサの速度になるわけではない。プロセッサとなると、大ざっぱにいって数十分の一から数百分の一くらいになってしまうが、それにしても、もの凄いスピードに違いない(1/100でも動作クロック26GHzのプロセッサになる!)。

このプロセスは単に微細というだけでなく、完全空乏型SOI構造を採り、かつゲート絶縁膜に高誘電率(High-k)の新材料を使っている。SOI構造だから基板への漏れ電流は原理的にはなく、さらに完全空乏型なのでスレショルド(threshold:「しきい」や「境界」のこと)電圧を下げてもソース、ドレイン間のリーク電流が抑えられる(「第10回 SOIは夢のテクノロジーか?」参照のこと)。またゲート絶縁膜が薄すぎるとゲートから流れてしまうリーク電流にも、High-kの絶縁膜に厚みを持たせることで対処できる。高速化で先頭を走るIntelが直面している「熱の壁」を打ち破るための特性が随所に採用された先端の研究開発である。

TeraHertzトランジスタの構造

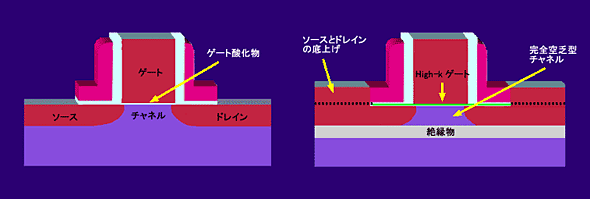

TeraHertzトランジスタの構造「New Transistors for 2005 and Beyond[PDF]」と題したTeraHertzトランジスタに関するプレゼンテーションより。左側が既存のMOSトランジスタの構造、右側がTeraHertzトランジスタの構造。ゲート絶縁膜のHigh-k採用や、完全空乏型のチャネル構造、さらにソースとドレインの幅を厚くすることで抵抗値を下げるといった工夫を行っている。今回開発したTeraHertzトランジスタには、絶縁体としてZrO2(二酸化ジルコニウム)を採用しているという。

TeraHertzトランジスタの写真

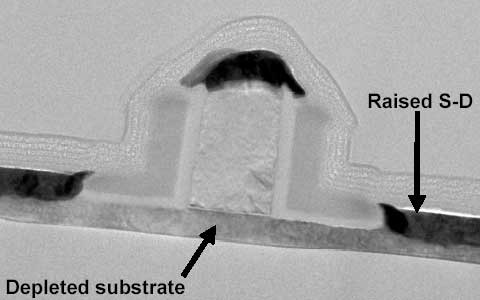

TeraHertzトランジスタの写真「New Transistors for 2005 and Beyond」より。Depleted substrate:空乏層、Raised S-D:ソースとドレインの底上げ。

TeraHertzは最先端だが新しくない

繰り返していうが確かに超最先端だ。そして最近のトレンドは全部押さえている。けれどトレンドというくらいで、Intelだけがやっているわけではない。まずSOI構造であるが、これは「第10回 SOIは夢のテクノロジーか?」でもすでに取り上げたくらいで、開発していない会社の方がむしろ少ないくらいである。その中で完全空乏型は、部分空乏型に比べシリコン層の厚みを1/3などと薄くしないとならないので、製造時のバラツキ制御が難しい。しかし、スレショルド電圧を下げられるので高速になるし、またスレショルド電圧を下げると普通のMOS(ソースとドレインの間の電流をゲートにかける電圧で制御する構造)では大問題になるリーク電流の増大が抑えられて低消費電力になる、という具合でSOIならではの利点が出しやすい。そのため、最近ではこちらに注力している会社が多いと聞いている。また、High-kであるが、こちらも微細化に伴いどの会社も採用を考えているようだ(一方、銅配線技術がらみではLow-kの新材料がトレンドなので、そちらと混同しないように……)。

MOSトランジスタというのは実際キャパシタ(コンデンサのような、電荷を蓄える素子のこと)でもあり、2枚の電極を絶縁膜で挟んだものなのだ。横に小さくする(微細化する)ときには縦にも同じように小さくしないと容量が確保できない。ただこれを進めると、現時点ですでに原子数十個分の厚みまで薄くなっているから、15nmといった長さに対応する厚みは原子数個になってしまうはずである。こうなると絶縁膜が絶縁でなくなって電流が流れてしまい、まともに信頼して長年使える膜にならない。そこで、高い誘電率の絶縁材料に変更して、厚い絶縁膜でも同じ容量が確保できるようにするわけである。

今回のIntelの発表は、極めてトレンディな流れの中で、Intelは先頭を走っているのだというアピールであり、12月の学会(インターナショナル・エレクトロン・デバイセズ・ミーティング)で発表するので、その前にリリースを出しておいた、ということであろう。また「TeraHertz」というネーミングと「ムーアの法則は不滅です」という感じの説明を繰り返しているのは、半導体の成長の頭打ちを懸念している株式市場へのアピールの意味合いが強いように思われる。半導体はもう駄目みたいな悲観的なことを書いちゃうコラムニストもいるからね。

実用化にはまだ問題が山積み

一応、手放しでは喜べない点も指摘しておく。研究レベルでトランジスタが作れたということと、実際に工場で大量生産して商売になる、というのはだいぶ違う。Intelのニュース・リリースを読んでいると、すぐに明日からでも作れそうな気になってくるが、実際はそうではない。Intelもよく分かっているとおり、4〜5年は当然、もしかするとその2倍くらいかかるかもしれないのだ。なにせトランジスタの製造にせよ、動作にせよ、物理現象が絡んでくるので、人間が決めたスケジュールどおりに開発が進むと思ったら大間違いだ。あるところで突然、物理現象による壁が立ちはだかるかもしれない。

たまたまうまく作れただけでも、それは研究にはなる。しかし量産となれば、バラツキはあっても、ある程度の収率に確実に収まらなければならない。SOIの完全空乏型では、薄いシリコン層を作るときに厚みがばらついてしまうのをどう抑制するか、ということを現在どこも頭を悩ませている最中と聞く。IntelのTeraHertzにせよ同じような問題は避けられないはずだ。そのうえ微細化に伴って、だんだんトランジスタが高層ビルのように縦に高くなってしまうので、いっそのこと横倒しにして作ろうか、といった冗談のような話も出ているくらいだ。量産という面では、さらなる技術革新が必要になるかもしれない。また、High-kにせよLow-kにせよ、これまで新材料の導入は一筋縄ではいっていない。やはり長年慣れ親しんで性質のよく分かっている酸化シリコンからの移行では、いろいろと問題が出てくるだろう。

そういったプロセス面での技術的な問題がクリアできたとしても、工場とその生産設備の問題がある。当然、いまの露光技術の延長では不可能な領域であるし、製造装置の開発にせよ工場ラインそのものにせよ、これから解決すべき問題は山のようにある。さらに、いまでさえ先端の製造ラインへの巨額の投資に多くの半導体会社があえいでいるのに、いったいいくらかかるのか想像もつかない。単純にいままでの延長線上で工場に金がかかるとすれば、その時代にはさすがのIntelといえども簡単には賄えない金額になるだろう。そういう点で、安い工場ラインの開発というのも解決すべき問題の1つになるだろう。さらに設計の立場からいわせてもらえば、設計ツール、設計技術面でも何段階か上の技術が必要になる。ようやくLSI内部のデジタル回路設計も高周波、分布定数回路的な挙動に直面せざるを得なくなってきている昨今である。この数十倍の集積度、周波数ともなると数世代進んだ設計技術が必要になりそうだ。

取りあえず、7〜8年後に主流になるべきトランジスタが動いたということで、先に明かりをともしてくれた発表ではあった。しかし、そこへ至る道筋には、いままで以上に高い障壁が横たわっており、実際にいつ、どれだけのものがそこに到達できるのかは皆目分からない。自信を持っているのはIntelだけかい?

■関連リンク

- TeraHertzトランジスタに関するニュースリリース(インテル)

- シリコン技術に関する情報ページ[英語](Intel)

- New Transistors for 2005 and Beyond[英語][PDF](Intel)

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.