第132回 「ムーアの法則」の延命を可能にする3次元トランジスタとは:頭脳放談

Intelが3次元構造を採用した新型トランジスタ「Tri-Gate」を発表。これでムーアの法則が延命できるとか。この新型トランジスタは何がすごいのか。

前回、Intelの「ムーアの法則」へのコダワリにチャチャを入れたからというわけではないだろうが、即座に切り返されてしまった。ご存じかと思うが「3次元構造のトランジスタを使ったプロセッサを商品化するぞ」という発表である(インテルのニュースリリース「インテル コーポレーション、3 次元構造を採用した新型トランジスターを実用化へ」)。これにはCore iシリーズに代表される主力プロセッサだけでなく、Atomのようなローエンド製品まで含まれるようだ。まさに「ムーアの法則」を堅持するのだ、というIntelの強い意志の表れだと思う(「ムーアの法則」が維持できなくなると、アナリストに「会社の将来性に対する黄信号」を勝手に点灯されてしまうという脅迫観念があるためかもしれないが)。

3次元といっても、トランジスタが立体的に何層も積み重なるようなものではない。いままではX-Y方向に広がっていたトランジスタ(Z方向はトランジスタの厚みがごく薄い)を、深さ方向であるZ方向(とXもしくはY方向)においた、というイメージである。たとえて言えば、いままでは平たいタイルを敷き詰めてあったものを、箱詰めで梱包されたタイルよろしく、90度回転して薄いタイルの端面を下にして立て、ギッシリ詰めこんだような形である。当然、いままで薄く広がっていたトランジスタの面積に何個ものトランジスタを詰め込むことができるので面積当たりの集積度は上がる。さらにそのとき、単に90度回転しておくだけでなく、いままではタイルの表面の1面だけにあった制御ゲートを側面側にも回り込ませて立体的に電流が通過するチャネルを包み込んだ、というところが技術的なミソである。

Intelが開発した3次元トランジスタ(Tri-Gate型トランジスタ)の模式図(Intelのプレゼンテーション資料より)

Intelが開発した3次元トランジスタ(Tri-Gate型トランジスタ)の模式図(Intelのプレゼンテーション資料より)制御ゲート(Gate)を側面にも回り込ませることで、立体的にチャネルを包み込んでいる点がミソである。

いままで2次元のトランジスタを作ってきた「プレーナ・プロセス」自体、Intelの創業者の1人であるロバート・ノイス博士(もう1人が「ムーアの法則」のムーア博士だが)の発明だから、Intelが「第2の(MOS)トランジスタの発明」だと声高にいうのも根拠なしとはいえない。しかし、横方向の広がりに限界が見えるなか、縦方向に活路を見出すことは、かなり前から模索されていた。実際、いち早く横の限界に直面したDRAMの容量部分は、相当前から縦の深さ方向に掘り込むのが主流となっている。そのおかげもあって、もともと印刷技術のように平面的であった半導体製造プロセスの中で「縦に掘る」製造技術が培われてきていたのだ。余談だがその効果はMEMSなどにも利用されている(MEMSについては「第43回使い古しの半導体工場はMEMSで生かせ?」参照)。今回のIntelの3次元のトランジスタもそのような製造技術の発展とは無縁とはいえないだろう。しかし、高速なロジック物のトランジスタで、それも商用の最先端のプロセッサに全面的に適用しようというのは、Intelが初めてだろう。

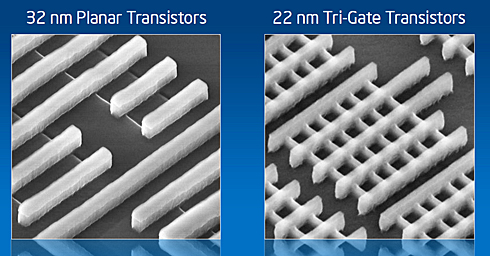

Planar型トランジスタとTri-Gate型トランジスタの比較(Intelのプレゼンテーション資料より)

Planar型トランジスタとTri-Gate型トランジスタの比較(Intelのプレゼンテーション資料より)既存のPlanar型トランジスタ(左)に対し、新たなTri-Gate型トランジスタは、垂直方向(Z方向)に対してゲートが構築されていることが写真からも分かる。

3次元のトランジスタと聞いて、即座に気になるのが熱の問題である。現状の先端プロセッサの発熱はすでに限界に近い。1トランジスタ当たりの発熱が同じまま集積度をアップすれば熱の問題に直面するに決まっている。そこで効果を発揮するとしているのが、平面的だった制御ゲートを立体的に3方向から取り囲む構造に変え、1トランジスタ当たりの発熱を抑えるという方法である。いってみれば1個1個のトランジスタの「締まり」を良くして電流を絞ること、で同じ面積に多数を詰め込んでも熱的問題に対処できるということのようだ。

ただし、動作クロックを上げれば発熱が増えるのは避けられない。それは1個1個のトランジスタの消費電力を減らしても同じである。トランジスタ1個が10分の1の発熱だとしても、10倍の集積度ならば単位面積当たりの発熱は同じだし、そこで動作クロックを2倍にすれば、単位面積当たりの発熱は2倍になってしまう。今回のプロセスを考えると、集積度を上げる方がよりイージーだ。

いままでも動作クロックは上げずに、コアの個数増加などにより並列度を上げて、性能向上を図る手法が定着していたが、この新プロセスでは、集積度向上を利用して並列度を上げる方向により傾くのではないだろうか。現状の1けた個数の並列度でなく、2けた、3けた程度まで並列度を高めるような実験的な試みがいくつか試されているが、このプロセスがそういった「新アーキテクチャ」の呼び水になることは十分考えられるだろう。場合によっては動作クロックを落としてでも集積度を生かした方がよいかもしれない。そういう点では、並列度を高める新アーキテクチャでなくとも、Atomのような低速だが機能を取り込んで高集積度という系統にも向きそうだ。

当然、今回の新プロセスにより集積度は向上する。よって「そろそろ限界か」とささやかれ続けてきた「ムーアの法則」の延命に貢献することは確実である。しかし、横のものを縦にしてギッチリ詰め込んだという「収納」原理によるものだから、その効果はせいぜい1けた、10倍くらいと考えられる。ムーアの法則的にいうならば、せいぜい3世代くらい限界を先延ばしにする程度の効果しかないだろう。Intelは、それだけの時間があれば、また次の「発明」を成し得ると思っているのかもしれないが……。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部を経て、現在は某半導体メーカーでRISCプロセッサを中心とした開発を行っている。

「頭脳放談」

Copyright© Digital Advantage Corp. All Rights Reserved.