多層ニューラルネットワークを1チップに多層構造で実装 東京大学生産技術研究所の小林正治氏らが3次元集積デバイスを開発:2次元配列の「配線問題」を解決

東京大学生産技術研究所の准教授を務める小林正治氏らは、IGZOトランジスタと抵抗変化型不揮発性メモリを3次元集積したデバイスの開発に成功した。ディープラーニングの多層ニューラルネットワークを1チップ上に多層構造で実装可能になる。

この記事は会員限定です。会員登録(無料)すると全てご覧いただけます。

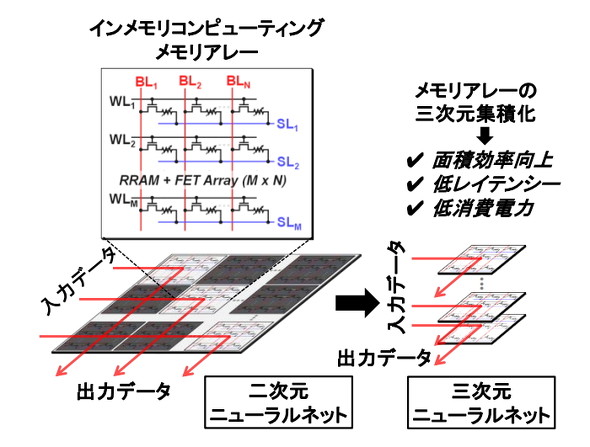

国立研究開発法人科学技術振興機構は2020年6月14日、東京大学生産技術研究所の准教授を務める小林正治氏らが、極薄のIn-Ga-Zn-O系酸化物半導体(IGZO)を用いたトランジスタと抵抗変化型不揮発性メモリ(RRAM)を3次元集積したデバイスの開発に成功したと発表した。メモリに演算機能を持たせたインメモリコンピューティングのハードウェア実装に関する課題を解決し、ディープラーニングの多層ニューラルネットワークを1チップ上に多層構造で実装可能になる。

2次元配列の「配線問題」を解決

多層のニューラルネットワークを構成するディープラーニングは、大量のデータ処理を必要とする。そのため従来のコンピュータでは、プロセッサとメモリの間のデータ転送速度に処理性能が左右されてしまう。

この課題を解決する方法として、プロセッサとデータをやりとりしない「インメモリコンピューティング」が期待されている。だが、通常のディープラーニング処理では2次元配列を使うため、ニューラルネットワークが大規模になるほどデータが通る「配線」が長くなり、計算の遅延や消費電力が増大してしまう問題があった。

小林氏らが開発したデバイスは、トランジスタとRRAMを3次元集積することで、2次元配列の配線問題を解決した。メモリを3次元積層して3次元ニューラルネットワークを構成することで、超並列計算も可能にする。半導体材料にはIGZOを用いて、通常の集積回路の配線層プロセスに適用可能な最高温度である400℃以下で、IGZOをチャネルとするトランジスタ(IGZOトランジスタ)とRRAMを形成した。開発したデバイスの各層は、RRAMとIGZOトランジスタによるメモリセルからなる配列で構成される。

小林氏らは、開発したデバイスによってインメモリコンピューティングの機能を、ニューラルネットワークの基本計算であるXNOR演算で実証した。具体的にはRRAMにニューラルネットワークの「重み」を学習させ、IGZOトランジスタのゲートにつないだワード線に入力データを印加。重みと入力データの組み合わせによってプリチャージしておいたビット線の電圧が放電され、XNOR演算の結果がビット線の出力電圧として得られた。小林氏らによると、定常電流を発生させないため、従来の方式に比べて10分の1以下の消費電力で演算可能だという。

この実証によって、ディープラーニングの多層ニューラルネットワークを1チップ上に物理的に多層構造で実装可能になる。小林氏らは「ディープラーニングを高いエネルギー効率で計算でき、クラウドだけでなくエッジデバイスでも高度な人工知能処理ができる」としている。

関連記事

ニューラルネットワークの学習でしていること

ニューラルネットワークの学習でしていること

シンプルな関数をニューラルネットワークに見立てて、その係数を学習させながら、その過程でどんなことが行われているかを見ていきます。 ディープニューラルネットワーク(DNN:Deep Neural Network)とは?

ディープニューラルネットワーク(DNN:Deep Neural Network)とは?

用語「ディープニューラルネットワーク」について説明。ニューラルネットワークをディープラーニングに対応させて、ネットワークの階層を深くしたもののことを指す。 ニューラルネットワークライブラリTensorFlow/Kerasで実践するディープラーニング

ニューラルネットワークライブラリTensorFlow/Kerasで実践するディープラーニング

最近流行の機械学習/Deep Learningを試してみたいという人のために、Pythonを使った機械学習について主要なライブラリ/ツールの使い方を中心に解説する連載。今回はニューラルネットワークのライブラリであるTensorFlow/Kerasについて解説します。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.