第271回 Intelの未来予想図? ムーアの法則は続くよ、どこまでも:頭脳放談

Intelが電子デバイスの学会「IEDM 2022」で、パッケージング上での10倍の実装密度向上を目指し、原子3個分の厚さの新素材でトランジスタの微細化を進める計画を発表した。果たして計画通りに進むのか、注目すべき点を解説しよう。

この記事は会員限定です。会員登録(無料)すると全てご覧いただけます。

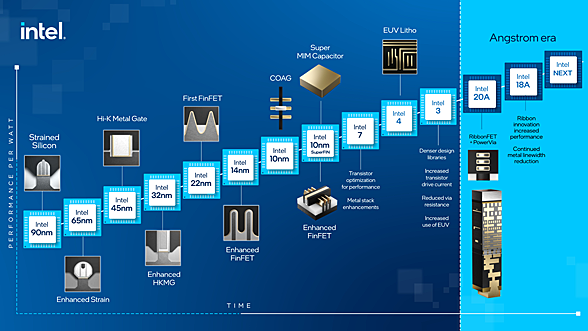

Intelが発表したトランジスタ開発の時系列

Intelが発表したトランジスタ開発の時系列Intelが2022年2月16日に公開したムーアの法則に関するホワイトペーパー(「Moore’s Law - Now and in the Future」)より。IEDM 2022では、この先についての発表が行われた。

10年先(英語でいう「the next decade」)の未来予測が話題になることはちょくちょくある。そういう書籍も出版されている。しかし、10年後にその未来予測の結果を検証するような記事には、お目にかかったことがほとんどない。結構「言いっぱなし」の予測が多いような気もしないでもない。

3つに分類できる未来予測

個人的には未来予測というものは、おおよそ同じ確率で3つに分類できると思っている。3分の1は大外れ、3分の1は当たりと外れが混ざっている、3分の1はあたらずといえども遠からず、というところ。ということは、外れる方が多いのか?

まず大外れの場合だ。予想するターゲットは、技術なのか、市場なのか、企業なのかは問わない。アレが来るかコレが来るかと、本命、穴馬を予想していたら、結局どちらもこなかったというケースである。ちゃぶ台返しかコペルニクス的転回か、予測時点では知らなかったか、存在すらしていなかった全く違うものが来てしまいました、というケースである。

何とはいわないが、こういう予想は度々あった気がするが、案外、大外れは責められない。「トレンド線の延長上で物事を予測する人間の性質上仕方がない」ともいえる。影も形もないものを未来予測しても、相手にされないことは必定だ。

また10年間には、一度くらい環境の激変はある。天変地異や恐慌に戦争、そういうものの影響は、致し方あるまい。といって、予測ハズレを正当化するのもどうかと思うが……。

当たりとハズレが相半ばするようなケースから、あたらずといえども遠からずまでは、実際はシームレス的で連続的かもしれない。しかしそこで感じるのは、人間相手の命題はまずハズレるが、物理現象相手の命題の予想は堅い、という傾向である。

10年後の人々が何をどう感じるのか予想するのは難しい。しかし物理現象が律速となっている技術の進歩を予想するのは比較的アタリやすいということだ。ただし、細かいハズレはままある。10年予想が15年になることなど多い。あんまり時間軸がずれると、諦められて大外れに転じることもあり得るのが怖い。

Intelが見る10年先の未来予測のポイント

さて、電子デバイスの学会であるIEDM 2022向けに、Intelが今後10年の未来予測的なリリースを出していた。「Intel Research Fuels Moore's Law and Paves the Way to a Trillion Transistors by 2030」である(Intelのプレスリリース「インテル・リサーチ、ムーアの法則を加速し、 2030年までに1兆トランジスター達成に向け前進」)。この期に及んでも、Intelはムーアの法則(Moore's Law)を諦めない。それはこの先10年も続く、というロードマップ的なリリースである。

このIntelの未来予測は、その奥底に物理現象が横たわっている。つまりは、ソコソコ当たる可能性が高いと思っている。リリースとは順番が逆になるかもしれないが、物理現象に近い下層の部分から眺めていきたい。

なぜIntelはFeRAMに注目するのか

電子デバイスに関心のある人であれば、Intelのプレスリリースの中で引っ掛かる部分の1つが「FeRAM」ではないかと思う。FeRAMは、不揮発のメモリデバイスである。別に新しい技術ではない。富士通など数社が長年実ビジネスを行ってきている。ニッチな用途の小規模なメモリ(すみません)である。

しかし、IntelがFeRAMを持ち出したのは、従来と異なるハフニウム系の強誘電体素材によってFeRAMを先端ロジックデバイスと混載できそうだからに他ならない。

何でFeRAMがあるとよいのか? それは「ダークシリコン」という言葉に関係している。「ダークシリコン」とは、先端の超高集積なSoCにおいて、ごく一部の回路だけが動いていて、多くの回路は待機状態にあるという問題だ(頭脳放談「第221回 今どきスマホのCPU『A12 Bionic』『Kirin 980』には暗黒面がいっぱい」参照)。FeRAMは、この「ダークシリコン」の問題に一石を投じることになるのだ。

全部を全部フル稼働させていたら、SoCなど過熱して溶けてしまう可能性もある。人間の脳とのアナロジーを考えてみたら納得いくかもしれない。人間の脳も一部だけが動いていて全部を一度に使っているわけではない。処理に必要な部分のみを活性化しているのであって、いつも全てが必要なわけではないからだ。

最近の大集積の半導体は、それに近い状況にあるともいえる。瞬間的に動作している部分はわずかで、他は待機状態の部分が多いのだ。ダークシリコンは集積度を上げれば必然に増える傾向にある。

ただ、待機状態というのは、そこにある記憶を保持したまま、いつでも必要に応じて動き出せるということに他ならない。動作クロックを落としたり、電圧を下げたりする技を駆使して、現状のロジック回路でも記憶を保持している。

それには待機電力が必要であることは想像できるだろう。微細プロセスではその電力もばかにならない。しかし記憶素子としてFeRAMが組み込まれていれば、完全電源断状態から即座に復帰できるようになるはずなのだ。

GaNの採用にも注目

もう1つ、Intelのプレスリリースの中に従来ロジックデバイスでは見なかった材料への言及がある。「GaN(窒化ガリウム)」だ。

これまた電子デバイスに関心のある人であれば、パワー系の高速スイッチングデバイスでお目にかかる材料、という認識じゃないかと思われる。これまた従前からあるけれど、畑違いで使われているものである。

しかしIntelは、この材料を先端のロジックデバイスに導入しようとしているようだ。それはなぜか。シリコンよりも高耐圧、高耐熱、高速といった利点があるからだ。

そんなパワー系に使われるような材料は、当然コストもかかり、先端微細プロセスとの融合は険しい道のりになりそうなのに、Intelはそれを求めている。その理由の1つが、次の10年後には、Intelいわく、膜の厚みが原子3個という微細さに到達しないとならないからだ。正直いって原子3個で大丈夫なのか、と思う。全部が3個ということもないだろうが、膜にかかる電圧が上がっていくのは想像がつく。シリコンのままではいられないという表明だろう。

Intelのプレスリリースには「GAA(gate-all-around)」などのトランジスタ構造も含まれているが割愛させていただく。

複合チップ化と3次元パッケージも当たり前になってくる?

上位レイヤーで、1つ注目したい言葉を選ぶと「quasi-monolithic(疑似モノリシック)」という言葉だ。現状の普通のチップは「monolithic (モノリシック)半導体」ということになる。それが「quasi(疑似)」ということは、「monolithic」に近いけれども、完全に「monolithic」ではない、ということだ。

つまり上記のような材料変更の荒業などを行っても、Intelの目指すムーアの法則の維持には足りない、ということなのだ。

結局のところ、現在既に行われているチップレットなどの複合チップ化と3次元のパッケージング技術を駆使し、複数個のダイを、さも1つのモノリシックデバイスであるかのように見せかけていかないとダメだということだ。

膜厚が原子3個の世界に到達した後も改良は続くだろうが、薄くする、縮小するといった方向での進歩は多分頭打ちになる。その先はこれまた人間の脳のように、3次元的に構成していくしか方法はないということだろう。

オリジナルのムーアの法則は、そんな3次元的な集積までスコープに入っていたとは思えない。最近のIntelによる法則の解釈は、明らかな拡大解釈だ。しかし、その線に乗っているのも事実である。

それにしても気になるのは、日本半導体の期待の星「Rapidus」だ(Rapidusについては、頭脳放談「第270回 日の丸半導体再び? 最先端半導体製造会社「Rapidus」への懸念」参照のこと)。5年後に最先端のプロセスを持つファウンダリを立ち上げるのだそうだ。

5年後に最先端プロセスでビジネスを始めたとして、その5年後には膜厚的にはほぼほぼ限界が視野に入ってくる。その先も検討しているのだろう。当然、IDEMでの発表は、全て熟知されているのに違いあるまいが……。

筆者紹介

Massa POP Izumida

日本では数少ないx86プロセッサのアーキテクト。某米国半導体メーカーで8bitと16bitの、日本のベンチャー企業でx86互換プロセッサの設計に従事する。その後、出版社の半導体事業部などを経て、現在は某半導体メーカーでヘテロジニアス マルチコアプロセッサを中心とした開発を行っている。

Copyright© Digital Advantage Corp. All Rights Reserved.